The GOF platform is comprised of four powerful functional components: GOF ECO, GOF Formal, GOF LEC, and GOF Debug.

GOF ECO is the flagship tool within the GOF platform, offering state-of-the-art technology and methodologies for functional netlist ECO. Whether you need to identify non-equivalent modules, fix non-equivalent points, or streamline the Implementation netlist, GOF ECO has you covered.

GOF Formal is another critical component of the GOF platform, providing a formal method for calculating fault coverage in an IC design in functional safety.

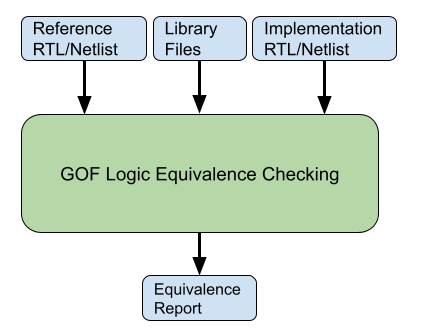

GOF LEC is the logic equivalence checker tool within the GOF platform, enabling users to easily verify the equivalence of their designs and ensure that they function as intended.

GOF Debug is the netlist debug tool integrated with incremental schematic, providing a fast and efficient way to identify and resolve errors in your netlist.

The AI Client is integrated into the GOF platform, allowing all functional components to leverage AI capabilities. It supports natural language-driven ECO operations, enabling users to describe changes in plain language. At each critical ECO stage, the GOF AI Client receives guidance from the Server on the next steps in the process.

GOF release package can be found in

https://nandigits.co/download.php

Please complete the form to request an evaluation license before downloading the application.

The tool supports Linux 64bits OS. Download the release package and unzip to a directory. Set 'the_64bit_install_path/GOF64/bin' in search path.

Visit https://nandigits.co/supports.php?type=license to request an evaluation license. Or email [email protected] for more information. Without license, the tool can support netlist size less than 500K bytes. There are two license modes, fixed node mode and floating node mode.

GOF ECO incorporates the following features:

GOF ECO utilizes various advanced ECO methodologies, as netlist ECO can vary significantly in terms of size and complexity across different cases and companies. To provide users with maximum flexibility, GOF offers a range of methodologies to choose from, allowing them to select one or multiple options based on the specific requirements of the changes involved.

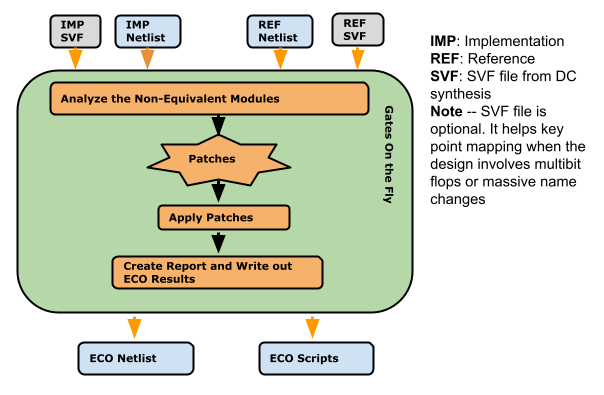

Figure 1: Complete Functional ECO Solutions

The automatic functional ECO is carried out using a GOF ECO script, which requires an Implementation Netlist that is currently under ECO and a Reference Netlist that is re-synthesized from the modified RTL with the same constraints as the pre-layout netlist. The 'fix_design' API is utilized to execute a top-down global ECO. GOF leverages its built-in Logic Equivalence Check engine to identify and analyze non-equivalent points in both the top-level module and its sub-modules. Logic patches are generated to rectify any non-equivalent modules, and the final patches are optimized circuits that minimize the gate count required to make the Implementation Netlist equivalent to the Reference Netlist. Finally, the 'map_spare_cells' API is used to map these patches to spare-type-gates.

If the ECO changes are limited in scope and size or involve repetitive operations such as adding inverts on a bus, it is more efficient to use the manual mode ECO. This mode is a better option as it results in fewer final gates being touched compared to automatic mode ECO. Additionally, both automatic and manual modes can be combined and executed within a single GOF ECO script.

When ECO is done in either automatic mode or manual mode, 'map_spare_cells' command is run to convert the newly added cells to spare gate types cells. Users can control only spare gate type cells being used in manual mode ECO, so that the converting stage can be bypassed. The flow supports both standard spare cells and gate array spare cells.

GOF supports hierarchical ECO by set the ECO scope to the sub-modules. Some Logic Equivalence Check cases can only be resolved in flatten mode. Since GOF only focuses on the modules or spots that user specifies, it can avoid to get false non-equivalence in hierarchical netlist.

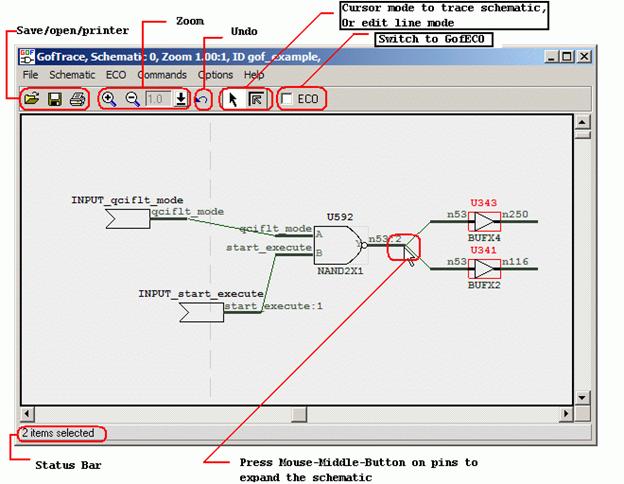

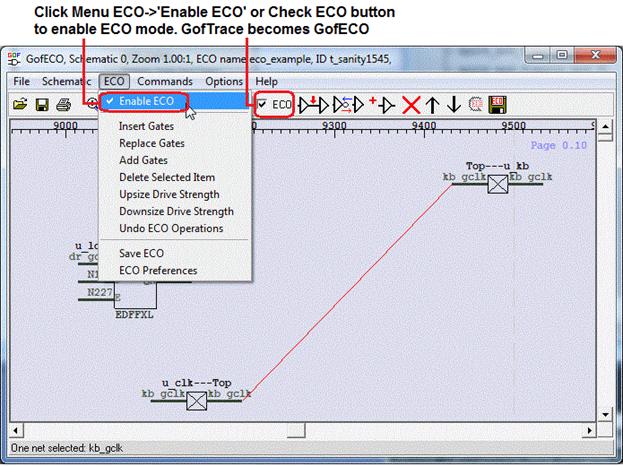

GUI mode ECO has advantage of fast ramping up. It's good for small size ECOs. The incremental schematic feature is very helpful for analyzing the netlist before the next step is decided.

The ECO modes listed above are integrated into one work environment seamlessly. The mixing of ECO modes can produce most optimal ECO result. For example, automatic ECO and manual script ECO can be done in one ECO script, so that the minimum size ECO patch can be achieved.

The Full Layers Functional ECO allows for the addition or removal of gates in a flexible manner. The ECO operations are performed using a script in Perl syntax, which accesses, modifies, and saves the netlist database using exported APIs. GOF ECO reads in two netlist files: the Implementation Netlist (which is under ECO) and the Reference Netlist (which is re-synthesized from modified RTL with the same constraints as the pre-layout netlist). In the ECO script, the 'fix_design' API is used to fix the top-level module and its sub-modules in global mode. GOF utilizes its built-in Logic Equivalent Check Engine to identify non-equivalent points and applies optimized minimum size gate patches to fix the non-equivalent modules.

Figure 2 shows that two logic cones are extracted from the Implementation and Reference Netlist for the same comparison point. Initially, the implementation point does not match the reference point. GOF compares the two points and generates a patch from the Reference logic cone, which it applies to the Implementation Netlist. After patching, the two points become equivalent.

Figure 2: Logic Cone Optimization

GOF performs logic cone analysis and optimization for each failing point discovered during top-down logic equivalence checks. The failing point takes the form of an output port or input pin of a sequential element, such as a flip-flop's D input. The final patch contains the fewest number of gates required to ensure that the implementation logic cone matches the reference logic cone.

Figure 3 depicts the flow chart of the process.

Figure 3: Automatic functional ECO flow

Steps for an automatic functional ECO:

The ECO script employs the exact syntax of a Perl script. It executes exported APIs that interact with the netlist database, facilitating modifications to the netlist.

The following is the example script for automatic functional ECO:

# GOF ECO script, run_example.pl use strict; setup_eco("eco_example");# Setup ECO name read_library("tsmc.5nm.lib");# Read in standard library # SVF files are optional, best to be used when the design involves multibit flops #read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format #read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module # Preserve DFT Test Logic set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design(); save_session("current_eco_name"); # Save a session for future restoration report_eco(); # ECO report check_design("-eco");# Check if the ECO causes any issue, like floating write_verilog("eco_verilog.v");# Write out ECO result in Verilog run_lec(); # Run GOF LEC to generate Formality help files write_compare_points("compare_points.report"); write_formality_help_files("fm_dir/formality_help"); # formality_help files are generated in fm_dir folder # fm_dir/formality_help.config.tcl can be used in Formality script to pass logic equivalence checking exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The ECO Script can be run by '-run' option.

Check Run and debug ECO script section in User Manual for more detail

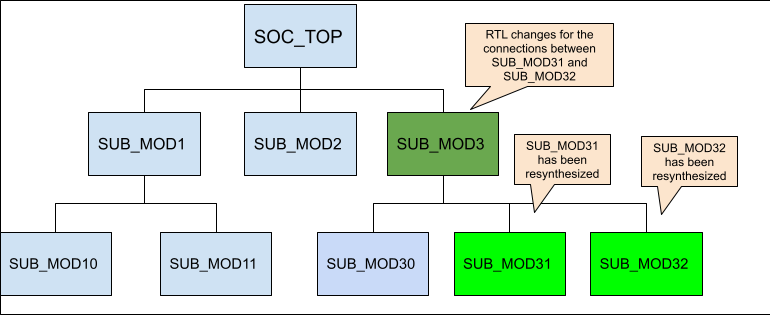

Performing a complete top-level netlist synthesis can be time-consuming. GOF provides APIs enabling the integration of newly synthesized sub-modules into the original pre-layout netlist, along with updates to the top-level SVF file. This incremental approach allows the generation of the large top-level netlist and the top-level SVF file, resulting in significant time and effort savings. At the RTL level, designers identify modified RTL modules during ECO and synthesize them to create netlist and SVF files. Some altered RTL modules, particularly sub-parent modules with only sub-module instantiations, may not require synthesis.

In Figure 4, only two sub-modules, SUB_MOD31 and SUB_MOD32, require re-synthesis in the extensive SOC_TOP design. Their parent module has only experienced connection changes and remains in netlist format, eliminating the need for synthesis. The example below illustrates how to process these files and generate a new SOC_TOP level netlist and SVF file.

Figure 4: Sub-modules to be synthesized

Step 1: Add missing DFT ports

The newly synthesized sub-modules may lack certain ports present in the original netlist. Notably, ports essential for scan in and scan out are typically added by the DFT tool. Since the DFT process is not applied to the new synthesized sub-modules, it's necessary to incorporate these ports as dummy ones within the modules to avoid syntax errors.

The procedure for incorporating DFT ports into the newly synthesized modules is as follows:

use strict; read_library("tsmc.lib"); read_design("-ref", "SOC_TOP.pre_layout.gv");# Read in the original pre_layout netlist read_design("-imp", "SUB_MOD31.new_syn.gv");# Read in new synthesized netlist set_tree("ref"); set_top("SUB_MOD31_1"); # The old pre-layout netlist may have this module with prefix or suffix added in uniquify my @ref_port_ins = get_ports("-input"); my @ref_port_outs = get_ports("-output"); set_tree("imp"); set_top("SUB_MOD31"); my @imp_port_ins = get_ports("-input"); my @imp_port_outs = get_ports("-output"); my $cnt = 0; foreach my $port (@ref_port_ins){ if(!grep($port eq $_, @imp_port_ins)){ # The input port is not in the new synthesized module new_port($port, "-input"); gprint("$cnt: Warning input $port is not in the new synthesized sub-module\n"); $cnt++; } } foreach my $port (@ref_port_outs){ if(!grep($port eq $_, @imp_port_outs)){ # The output port is not in the new synthesized module new_port($port, "-output"); gprint("$cnt: Warning output $port is not in the new synthesized sub-module\n"); $cnt++; } } write_verilog("SUB_MOD31.dft_ports_added.gv"); exit;

The identical process should be executed on SUB_MOD32 to include the necessary DFT-related ports.

Step 2: Replace sub-modules netlist and SVF

During this step, the DFT ports added netlist and SVF files of the synthesized sub-modules are read to substitute the original pre-layout netlist and SVF files.

The procedure for replacing netlist and SVF:

read_library("tsmc.lib"); read_svf("-imp", "SOC_TOP.pre_layout.svf"); read_design("-imp", "SOC_TOP.pre_layout.gv"); read_sub_module_svf("SUB_MOD31.svf.txt", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_svf("SUB_MOD32.svf.txt", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD31.dft_ports_added.gv", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_netlist("SUB_MOD32.dft_ports_added.gv", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD3.new.v", "-module", "SUB_MOD3_1", "-syn_module", "SUB_MOD3", "-sub_only"); # Need sub_only option replace_sub_module_netlist("SOC_TOP.new_reference.gv"); # Replace netlist should be run first replace_sub_module_svf("SOC_TOP.new_reference.svf"); # Then replace SVF

After the generation of both the top-level netlist and SVF files, they can be incorporated into the complete top-level automatic ECO process.

When working with designs that include multibit flops or significant name changes, SVF files can be a valuable tool for facilitating key point mapping. Although multibit flops are used to reduce silicon area and power consumption, the different combinations of single bit flop instances in each multibit flop instance can create challenges for key point mapping, especially when combined with name changes. Additionally, backend tools may split or merge multibit flops, further complicating the process. To avoid these challenges and ensure accurate key point mapping, it's highly recommended to load SVF files when working with multibit flops. For more information on this topic, please refer to the Multibit Flops in ECO section.

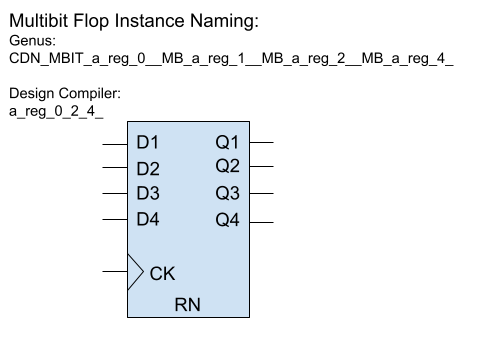

Multibit flops can pose a challenge in logic equivalence check and ECO due to the different naming conventions used by various synthesis tools. For example, as depicted in Figure 5, a four-bit multibit flop has a different naming style in Cadence Genus compared to Synopsys Design Compiler after name changing. Additionally, backend tools may split some multibit flops into single bit flops to address timing issues. These factors make key point mapping a complex task.

In logic equivalence check, multibit flops need to be mapped to single flops. However, the mapping of single flops to multibit flops from the Reference Netlist may differ from the Implementation Netlist. For instance, in Figure 5, the Implementation Netlist has a four-bit multibit flop instance named 'a_reg_0_2_4_', whereas the Reference Netlist after Synthesis may have two-bit multibit flops named 'a_reg_0_1_' and 'a_reg_2_4_'. Depending solely on naming conventions may not lead to the correct multibit to single bit mapping. Although LEC and ECO tools can handle some limited multibit to single bit mapping using comprehensive algorithms, there is no guarantee of complete successful mapping.

Figure 5: Multibit flop naming in synthesis tools

GOF provides support for accurate and reliable key point mapping through the use of text mode SVF files from Design Compiler. These SVF files are encrypted by default, but can be converted to text mode when using Formality to read the encrypted file. Additionally, GOF can convert backend multibit flop split/merge information into an SVF file. By reading both the synthesis SVF and the converted SVF file, GOF is able to completely resolve the mapping of multibit flops to single bit flops.

For instance, Innovus generates a multi_bit_pin_mapping file to store split and merge information. This file can be converted to an SVF text file using a GOF script.

Here is an example script for converting an Innovus multi_bit_pin_mapping file:

read_library("libdir/art.lib"); set_multibit_blasting(0); # Disable multibit blasting read_design('-imp', "imp_net.v"); set_top("the_top"); open(FIN, "./multi_bit_pin_mapping"); my $mbit_split = {}; my $mbit_merge = {}; while(<FIN>){ my ($from, $to) = (m/(\S+)\s+(\S+)/); $from =~ s/\/\w+$//; # remove the pin $to =~ s/\/\w+$//; my ($module, $to_inst) = get_resolved($to); my ($from_inst) = ($from =~ m/([^\/]+)$/); my $libcell = get_ref($to); gprint("get ref of $to as $libcell\n"); my $is_ff = is_seq($libcell, "-ff"); if($is_ff){ if(is_seq($libcell, "-bank")==0){ if(!exists $mbit_split->{$module}{$from_inst}){ $mbit_split->{$module}{$from_inst} = []; } if(grep($_ eq $to_inst, @{$mbit_split->{$module}{$from_inst}})==0){ gprint("Multibit split in $module $from_inst to $to_inst\n"); push @{$mbit_split->{$module}{$from_inst}}, $to_inst; } }else{ # Bank if(!exists $mbit_merge->{$module}{$to_inst}){ $mbit_merge->{$module}{$to_inst} = []; } if(grep($_ eq $from_inst, @{$mbit_merge->{$module}{$to_inst}})==0){ gprint("Multibit merge in $module $from_inst to $to_inst\n"); push @{$mbit_merge->{$module}{$to_inst}}, $from_inst; } } } } close(FIN); my $svf = ""; foreach my $module (keys %$mbit_merge){ $svf .= "guide_multibit -design $module -type { svfMultibitTypeBank } \\\n"; $svf .= " -groups { \\\n"; foreach my $mbit_inst (keys %{$mbit_merge->{$module}}){ my $i_st = ""; my $cnt = 0; foreach my $s_bit (@{$mbit_merge->{$module}{$mbit_inst}}){ $i_st .= " $s_bit 1"; $cnt++; } $i_st .= " $mbit_inst $cnt"; $svf .= "\t{ $i_st } \\\n"; } $svf .= " }\n"; } foreach my $module (keys %$mbit_split){ $svf .= "guide_multibit -design $module -type { svfMultibitTypeSplit } \\\n"; $svf .= " -groups { \\\n"; foreach my $mbit_inst (keys %{$mbit_split->{$module}}){ my $i_st = ""; my $cnt = 0; foreach my $s_bit (@{$mbit_split->{$module}{$mbit_inst}}){ $i_st .= " $s_bit 1"; $cnt++; } $i_st = " $mbit_inst $cnt $i_st"; $svf .= "\t{ $i_st } \\\n"; } $svf .= " }\n"; } open(FOUT, ">backend_multibit.svf.txt"); print FOUT $svf; close(FOUT);

Two SVF files for Implementation are loaded in the implementation read_svf:

read_svf("-ref", "reference.svf.txt"); read_svf("-imp", "implementation.svf.txt", "backend_multibit.svf.txt"); # Two SVF files are loaded read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO

The synthesis of a large SOC design is known for its time-intensive nature, often taking several days to complete. In cases where a functional ECO is necessary, particularly concerning a specific sub-module, the design team opts to confine the ECO to that particular sub-module instead of initiating synthesis for the entire design. Following this, the ECO results for the sub-module are retargeted onto the full top-level netlist. This strategy significantly accelerates the turnaround time and ensures the project schedule remains on track.

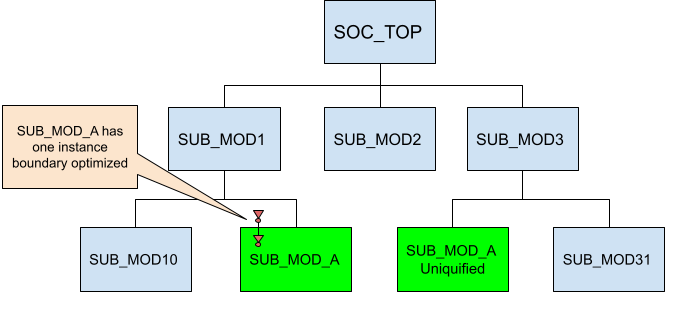

However, the team must factor in the boundary optimization of the sub-modules during backend processing. A given sub-module may have undergone unique transformations, resulting in the creation of multiple distinct physical modules with diverse backend optimizations. Illustrated in Figure 6, an instance of SUB_MOD_A may exemplify a backend modification, such as a port inversion.

Consequently, the automatic ECO process must be designed to account for these variations in backend processing, ensuring a comprehensive and accurate adaptation to the specific characteristics of each sub-module.

Figure 6: Instances of one sub-module have different boundary optimization

The boundary optimization challenge in GOF is addressed by incorporating the original pre-layout netlist. This is possible because the pre-layout netlist should mirror the state of the netlist before any ECO is implemented, with the boundary remaining unchanged prior to the placement and routing phase.

To extract the boundary optimization of sub-modules during ECO, a comparison is made between the pre-layout netlist and the netlist under ECO. As the automatic ECO is applied to individual sub-modules, the relevant boundary optimization information is retroactively annotated. This ensures the precision of the ECO and establishes equivalence when comparing top-level designs.

The loading of the pre-layout netlist is facilitated by using the "-ori_syn" option in the "read_design" command.

ECO retargeting script:

read_design('-ref', "new_sub_mode_a.gv"); # New synthesized sub-module-A read_design('-imp', "post_layout.gv"); # Full post layout netlist read_design('-ori_syn', "pre_layout.gv"); # Full prelayout, equal to post_layout.gv # Apply ECO to the first instance set_top_ref("SUB_MOD_A"); # Must set REF scope set_top("SUB_MOD_A_0"); # Uniquified name for the first instance fix_design; # Apply ECO to the second instance set_top_ref("SUB_MOD_A"); # Must set REF scope set_top("SUB_MOD_A_1"); # Uniquified name for the second instance fix_design; set_top("SOC_TOP"); report_eco(); write_verilog("post_layout.eco.gv"); # Full post layout netlist after ECO

This entire retargeting procedure is notably more time-efficient compared to performing a full netlist ECO. With the boundary information being meticulously addressed, the resulting ECO is highly accurate.

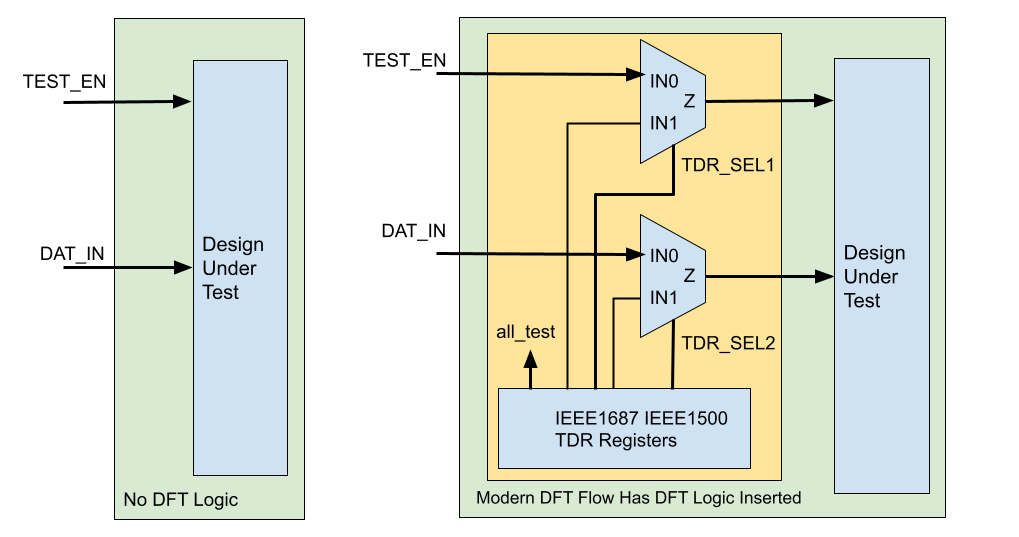

To prevent false non-equivalence in LEC and ECO, constraints must be placed on the DFT logic. In the traditional DFT flow, the DFT logic is typically incorporated into the RTL design, which appears in both the Reference Netlist and the Implementation Netlist. In contrast, the modern DFT flow, which supports IEEE1687 and IEEE1500 standards, inserts the DFT logic into the Implementation Netlist using a DFT tool like Mentor Tessent. To ensure that the Implementation Netlist, which contains DFT logic inserted by the DFT tool, matches the Reference Netlist, which lacks DFT logic, a Logic Equivalence Check must be performed. To prevent redundant or false ECO fixes, the DFT logic must be correctly constrained in the automatic functional ECO process.

In the traditional DFT flow, as illustrated in the left side of Figure 7, constraints are placed on the ports. For instance, DFT control signals such as TEST_EN are set to zero, while the normal functional ports are left unconstrained.

Figure 7: DFT Constraints in Automatic Functional ECO

In the modern DFT flow, these inserted DFT logic by the DFT tool as shown in the right side of Figure 7 should be constrained to be in inactive state. The control signals driven by TDR registers should be constrained to zeros.

GOF provides several APIs to constrain the DFT logic, set_ignore_output, set_pin_constant and set_net_constant. The API set_net_constant can be used to constrain the TDR registers signals. Since TDR registers are not ports, so they have be treated as nets.

The full script with constraints on the traditional DFT flow is shown below:

The full script with constraints on the modern DFT flow is shown below:

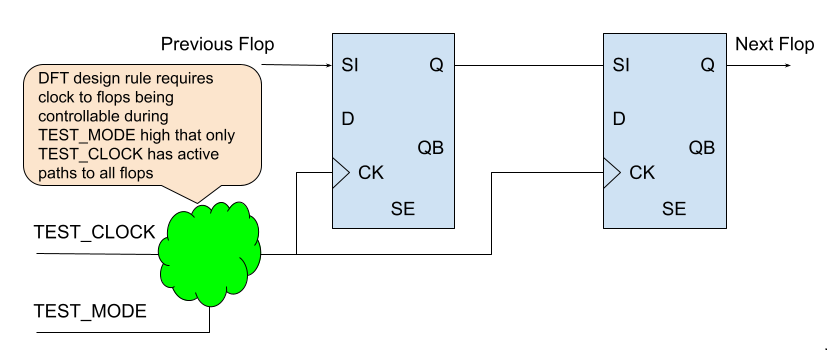

It's common for DFT logic to be broken during functional ECO processes, which involve modifying a design for functional reasons after it has already been verified. Since DFT control signals are disabled during functional ECO, the ECO tool is not aware that DFT logic has been modified and cannot verify its functionality. When the modified netlist is ready to be tested using DFT tool, it can take a long time to identify issues. GOF provides a fast DFT Design Rule Checker that can quickly identify issues with DFT logic. A fundamental design rule for DFT is to ensure that the scan chain is complete, meaning that it can be used to capture and output test patterns during testing. Additionally, clock and reset signals should be controllable during test mode to enable proper test pattern application.

Figure 8: DFT Design Rule Checker

The script to do DFT Design Rule Check:

set_log_file("dft_drc.log"); # Set log file name read_library("art.5nm.lib"); # Read in liberty file read_design('-imp', 'dft_top.v'); # Read in the design with DFT implemented set_top("DFT_TOP"); # Set the top module name set_pin_constant("test_scan_shift", 1); # Set scan shift pin to 1 set_pin_constant("all_test_reg/Q", 1); # Set TDR all_test register Q to 1 set_pin_constant("test_mode_reg/Q", 1); # Set TDR test_mode register Q to 1 create_clock("occ_add_1_inst/U0/Z", 10); # Set clock on OCC drivers, maybe multiple create_clock("occ_add_2_inst/U0/Z", 10); # Set clock on OCC drivers, maybe multiple create_reset("power_on_reset", 0); # Set reset pin set_top("DESIGN_TOP"); # pin_si/pin_so is internal pins of DFT_TOP set_scan_pairs("pin_si[0]", "pin_so[0]"); # Add scan chain pair 0 set_scan_pairs("pin_si[1]", "pin_so[1]"); # Add scan chain pair 1 # More scan chain can be added. These codes can be handled by a for loop command set_top("DFT_TOP"); my $err = dft_drc; if($err){ gprint("DFT DRC found $err errors\n"); }

The Design Rule Checker can catch these issues by error codes:

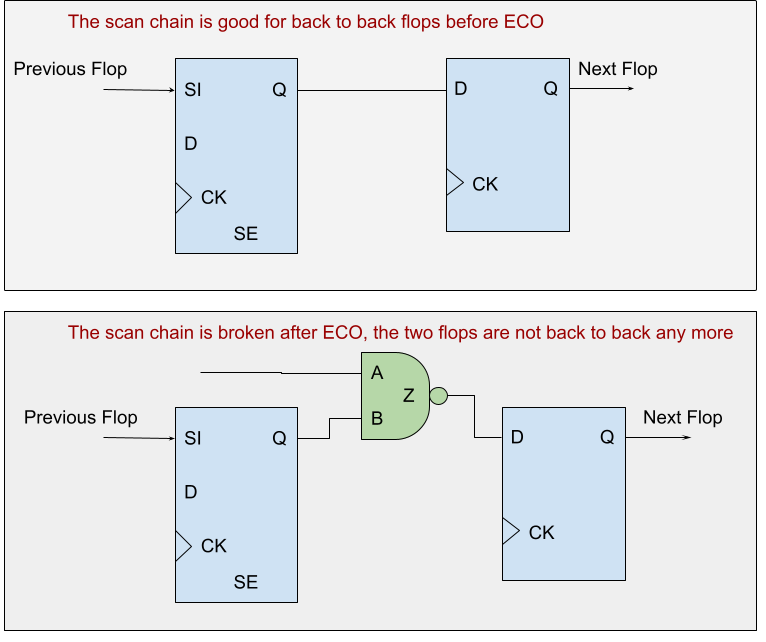

For instance, DFT DRC catches ERROR_MULTI_PATHS error in a functional ECO when an NAND gate is inserted between back-to-back flops.

Figure 9: Broken scan chain in functional ECO

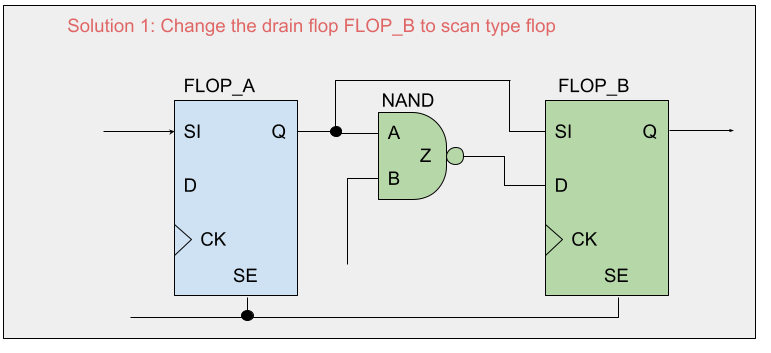

There are two solutions to fix the error. The first solution involves changing the drain flop, FLOP_B, to a scan type flop with scan_in and scan_enable pins.

Figure 10: Solution 1 to change the drain flop scan type

The second solution involves inserting a MUX before the D input of FLOP_B. The selection signal of the MUX is controlled by the scan_enable signal to select the output of the previous flop, FLOP_A, when scan_enable is asserted.

Figure 11: Solution 2 to insert a MUX to fix the scan chain

Both solutions can be implemented using GOF in either GUI mode ECO or script mode ECO. After the necessary fixes have been made, the DFT DRC will be free of errors.

For more information on GUI mode ECO, please refer to this page.

The commands to fix the logic in script mode:

#Solution 1 change_gate("FLOP_B", "SDFFHQX1", ".SI(FLOP_A/Q),.SE(FLOP_A/SE)"); #Solution 2 change_pin("FLOP_B/D", "MX2X4", "u_dft_eco_mux", "-,FLOP_A/Q,FLOP_A/SE");

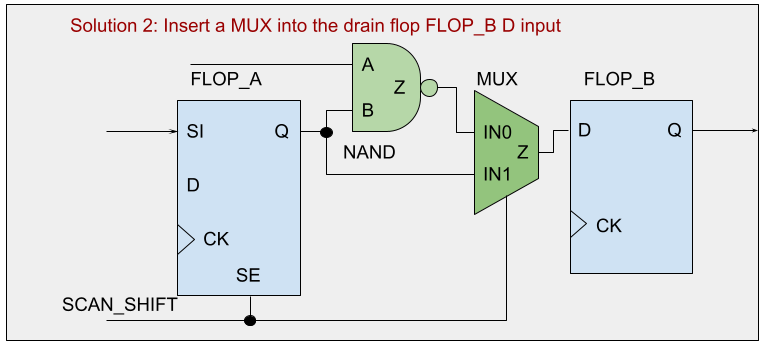

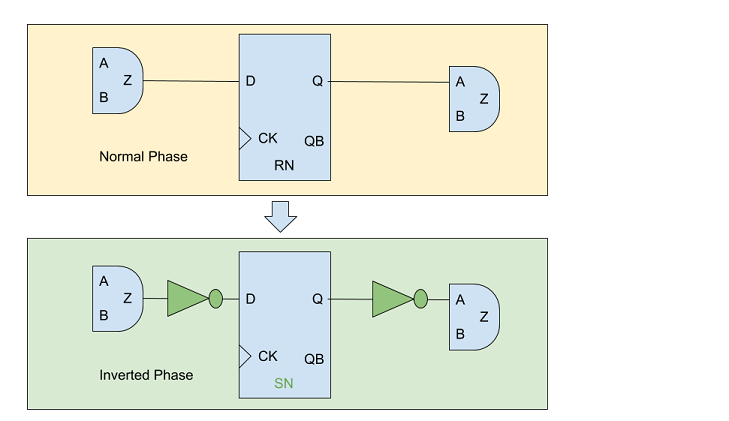

Physical Synthesis is more and more popular in logic synthesis. Physical Synthesis tool, Design Compiler Topographical(DCT) or Design Compiler Graphical(DCG) for example, may add hierarchical pins that are not in RTL code and it may cause mapping issue when Implementation Netlist is comparing with Reference Netlist in ECO.

For example, DCT may add 'IN0', 'IN1', 'IN2', 'IN2_BAR' ... to hierarchical modules. The new added pins are not necessarily matching to each other in Implementation Netlist and Reference Netlist. That is, IN0 in module A in Reference Netlist maybe a different signal from IN0 in module A in Implementation Netlist.

Figure 12: No Exact Pin Match

These pins are randomly named in each run. They won't affect logic equivalence check, but they need to be excluded in pin matching in ECO. Otherwise, the ECO tool would insert redundant logic or wrong logic.API set_noexact_pin_match can be used to resolve the mapping issue between Implementation Netlist and Reference Netlist.

By adding the port naming regular expression in the API argument, set_noexact_pin_match('\bIN\d+(_BAR)?\b'), these ports will be remapped.

Note: This API should be run before reading designs.

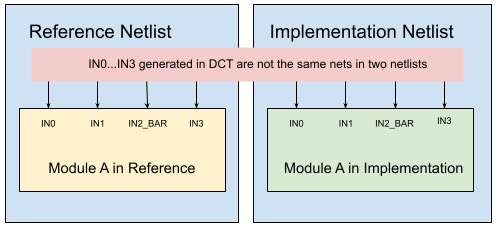

During the pre-mask design stage, transitioning a flip-flop from resettable to settable type or vice versa is a relatively straightforward task. However, making such changes during the post-mask design stage can be challenging because it can be difficult to locate an available spare flip-flop to replace the original one. To overcome this challenge, a common approach is to add inverters to the input and output pins of the flip-flop while maintaining its original set/reset type.

Aside from resolving the issue of locating spare flip-flops, adding inverters to the flip-flop input and output pins can also address timing or power-related concerns. In some cases, this technique can help with timing closure or reduce power consumption.

It is essential to note, however, that implementing such changes can lead to challenges during logic equivalence checking. Incorrectly addressing these changes can result in false non-equivalent points, leading to design uncertainty. As such, appropriate measures should be taken to ensure that the changes made to the flip-flop type do not affect logic equivalence checking.

Figure 13: Flip-flop Phase Inverted

To address this issue, the GOF platform provides an API command to configure these cases. The set_mapping_method('-phase') API is utilized to handle such situations and ensure that the changes made to the flop type do not cause false non-equivalent result.

By default, GOF uses 1'b0 for tie low net and 1'b1 for tie high net. Some designs may prefer tie cell over 1'b0/1'b1. API set_tiehi_net and set_tielo_net can be used to control which tie format is used. To overwrite the default 1'b0/1'b1, simply set empty argument to the APIs.

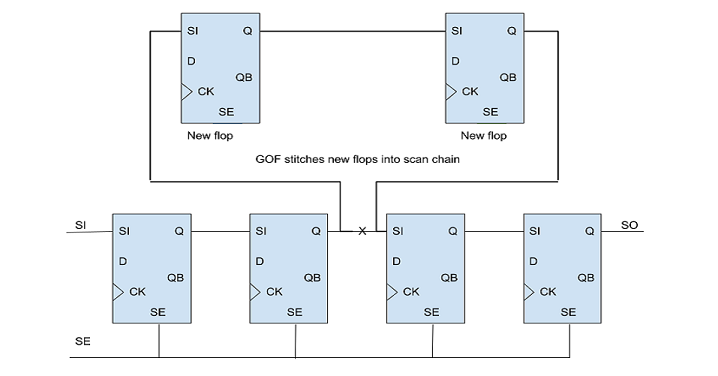

To prevent any loss of DFT coverage, it is recommended to integrate new flops added in an ECO into the existing scan chains. Industrial data suggests that in a design with 100K flops, 100 newly added non-scan flops can lead to a DFT coverage loss of over 0.1%. Such loss of DFT coverage is unacceptable for high-reliability chips, such as those used in automobiles. Therefore, if there are any new flops introduced in a functional ECO, it is necessary to redo the scan chain to incorporate the new flops.

Figure 14: Stitch scan chain

There are multiple methods available in GOF to insert new flops into scan chains. One option is to utilize the 'stitch_scan_chain' API, which automatically integrates the new flops into the scan chains. Alternatively, there are several netlist processing APIs that can be used to manually insert the new flops into the scan chains.

Automatic mode to insert flops into a scan chain in the local modules

An automatic method can be used to integrate flops into a scan chain within local modules. In the following example script, suppose the 'fix_design' command adds eight new flops named 'state_new_reg_0' to 'state_new_reg_7'. To integrate these flops into the scan chain within the local module:

Automatic mode to insert flops before one flop

GOF offers an automatic method to insert new flops before a specified flop instance. Users can identify the instance name of one flop, and GOF will insert all new flops into the scan chain before that instance.

For instance, let's say it is required to integrate all the new flops into the scan chain prior to the instance named 'u_pixel_ctrl/pulse_reg':

Manual mode to connect up all new flops

The scan chain can be re-connected up manually by ECO APIs. And new scan in/out ports are created.

# GOF ECO script, run_manual_stitch_scan_chain_example.pl use strict; undo_eco; # Discard previous ECO operations setup_eco("eco_manual_stitch_scan_chain_example");# Setup ECO name read_library("art.5nm.lib");# Read in standard library read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design; save_session("current_eco_name"); # Save a session for future restoration set_error_out(0); # Don't exit if finds error my @flops = get_cells("-hier", "-nonscan"); # Find all new flops that are not in scan chain yet # @flops can be defined by reading a list file if(scalar(@flops)){ # If there are new flops, start the work new_port("so1", "-output"); # New a scan out port so1 new_port("si1", "-input"); # New a scan in port si1 my $cnt = 0; my $now_si; foreach my $flop (@flops){ $cnt++; if(is_scan_flop($flop)==0){ my $flop_name = get_ref($flop); my $scanflop = get_scan_flop($flop_name); # If the flop is not scan type, change to scan type flop change_gate($flop, $scanflop); } if($cnt==1){ change_port("so1", "$flop/Q"); # The first flop drives the new scan out port }else{ change_pin($now_si, "$flop/Q"); } $now_si = "$flop/SI"; change_pin("$flop/SE", "te"); # All scan enable pin is connected to scan enable signal } change_pin($now_si, "si1"); # The last flop has the new scan in port driving SI pin } write_verilog("eco_verilog.v");# Write out ECO result in Verilog exit;

The module mentioned in the section above can have hierarchy kept instead of flatten, and being written into ECO netlist as whole. This flow needs the module and its sub-modules written out in a separate verilog file, then uses read_library to load the file with '-vmacro' option. GOF treats the module as a leaf cell.

An example for adding a new module:

The content in file syn_macro.v is written into the ECO file eco_verilo.v as a whole. The corresponding instance is created as well with ports connected correctly according to Reference Netlist.

When modifying RTL and do re-synthesis, care should be taken to maintain the database as much alike Implementation Netlist as possible.

A common problem in modifying RTL is having sequential signal name changed, which appears in Reference Netlist as a different flop instance. For example

It creates a flop instance 'abc_reg' in synthesis. If the ECO in RTL change this to

After synthesis, a new flop instance 'abc_new_reg' is created. GOF may fail to find that 'abc_new_reg' being able to merge with 'abc_reg', due to other non-equivalent points present, which brings a redundant fix in the new register creation.

So it is highly recommended to keep the sequential signal names in re-synthesis.

When do re-synthesis, the same constraints should be used as what has been used in Implementation Netlist synthesis. If any hierarchy is not present in Implementation Netlist, it's better to flatten the module in synthesis to maintain the same hierarchies.

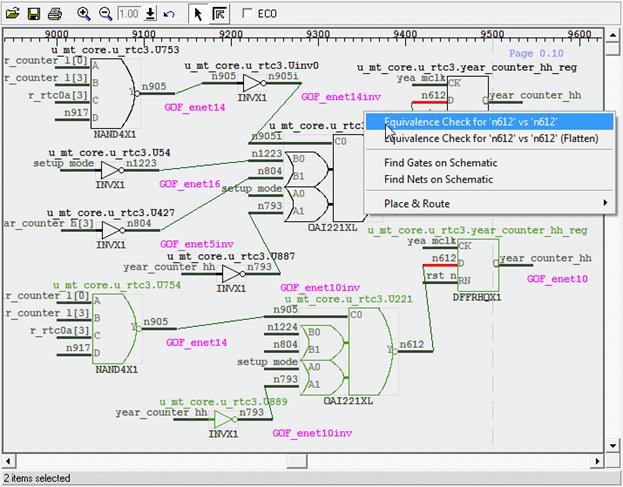

It happens that an ECO doesn't pass logic equivalence checker, especially for a large ECO. GOF can run individual logic equivalence checking for flop pairs, output port pairs or any two nets. Check annotating to schematic for more detail.

It is highly recommended to run 'check_design' after ECO, to speed up, users can specify '-eco' option,

It can detect if there is any floating or multiple drivers after ECO.

GOF LEC logic equivalence checking can be performed on any two netlists or on the results after GOF ECO run. Subsequently, Formality help files can be generated for use in Formality, significantly enhancing the success rate of the Formality tool.

Formality help files generation:

read_library("tsmc.lib"); read_design("-ref", "reference.v"); # Reference netlist read_design("-imp", "eco_netlist.v"); # ECOed netlist set_top("CHIP_TOP"); run_lec(); # Run GOF LEC write_compare_points("compare_points.report"); write_formality_help_files("fm_dir/formality_help"); # formality_help files are generated in fm_dir folder

In the above example, the assistance configuration file "fm_dir/formality_help.config.tcl" contains a compilation of set_user_match, rewire_connection, and set_constant commands designed to aid Formality in successfully achieving logic equivalence checking.

Integrate the file into Formality script:

# Formality netlist vs netlist script read_db -tech tsmc.db read_verilog -r reference.v read_verilog -i eco_netlist.v #Setup constraint #Read in the help config file source fm_dir/formality_help.config.tcl match verify

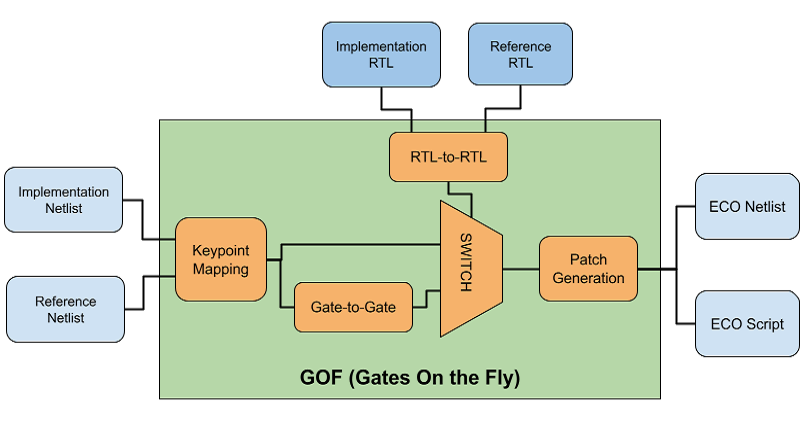

RTL-guided ECO employs two approaches: utilizing the built-in RTL logic equivalence checking engine of GOF or incorporating results from third-party LEC tools to pinpoint areas needing ECO adjustments. The advantage of the internal RTL LEC is its speed and efficiency. However, a drawback arises when hierarchies mismatch with synthesized netlists, particularly in designs with extensive SystemVerilog statements. To address this, third-party RTL LEC tool results can be utilized to resolve hierarchy inconsistencies. For example, GOF ECO can process a list file of non-equivalent results from tools like Synopsys Formality, allowing it to concentrate ECO efforts solely on identified areas.

The RTL Guided ECO Flow is an additional step in the netlist ECO process, which involves comparing RTL designs to identify any discrepancies. Unlike Gate to Gate comparison, this method is faster and more targeted. The ECO process can be slowed down by the insertion of DFT logic and boundary optimization, making gate-to-gate comparison more complicated. Additionally, the use of RTL comparison can prevent the generation of redundant ECO fixes during patch generation.

Figure 15 illustrates how RTL to RTL comparison runs parallel to the key-point mapping of two gate-level netlists. If the non-equivalent points identified by RTL comparison have been integrated into the ECO flow successfully, gate-to-gate comparison can be bypassed.

Figure 15: RTL Guided ECO Flow

GOF script has the exact same syntax as Perl script and runs the exported APIs that access the netlist database and modify the netlist.

The following is the example script for RTL guided ECO:

# GOF ECO script, rtl_guided.pl use strict; setup_eco("rtl_guided_eco_example");# Setup ECO name read_library("art.5nm.lib");# Read in standard library my $rtl2rtl = 1; if($rtl2rtl){ set_define("SYNTHESIS"); set_define("NO_SIM"); set_inc_dirs("/project/nd900/vlib/include", "/project/nd900/IPS/include"); read_rtl('-ref', "ref0.sv", "ref1.sv", "ref2.sv"); read_rtl('-imp', "imp0.sv", "imp1.sv", "imp2.sv"); set_top("topmod"); rtl_compare; } read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module # Preserve DFT Test Logic set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design; save_session("current_eco_name"); # Save a session for future restoration report_eco(); # ECO report check_design("-eco");# Check if the ECO causes any issue, like floating write_verilog("eco_verilog.v");# Write out ECO result in Verilog exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

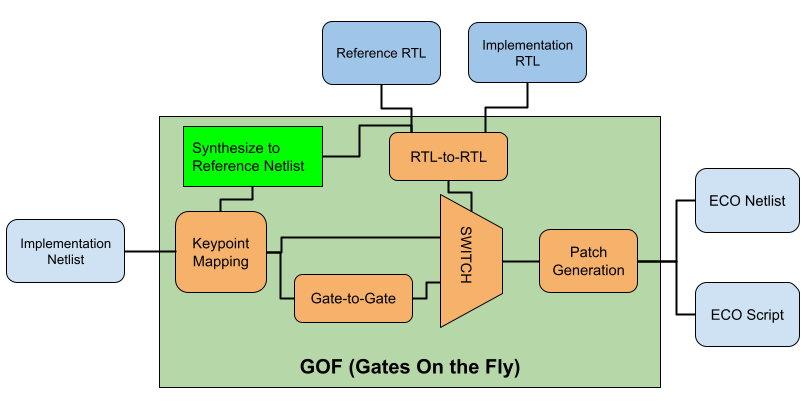

If Reference Netlist is not provided, it can be synthesized from Reference RTL by 'synthesize' command.

As shown in Figure 16, Reference RTL is directly synthesized into Reference Netlist and used in the ECO.

Figure 16: RTL Guided ECO Flow

The following is the example script for Reference RTL synthesis in RTL guided ECO:

# GOF ECO script, rtl_guided_synthesis.pl use strict; setup_eco("rtl_guided_eco_example");# Setup ECO name read_library("art.5nm.lib");# Read in standard library set_define("SYNTHESIS"); set_define("NO_SIM"); set_inc_dirs("/project/nd900/vlib/include", "/project/nd900/IPS/include"); read_rtl('-ref', "ref0.sv", "ref1.sv", "ref2.sv"); read_rtl('-imp', "imp0.sv", "imp1.sv", "imp2.sv"); set_top("topmod"); rtl_compare; read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module elaborate; # The command synthesizes the Reference RTL to Reference Netlist # Preserve DFT Test Logic set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design; save_session("current_eco_name"); # Save a session for future restoration report_eco(); # ECO report check_design("-eco");# Check if the ECO causes any issue, like floating write_verilog("eco_verilog.v");# Write out ECO result in Verilog exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

GOF ECO has the capability to ingest a list of ECO points, enabling it to concentrate exclusively on the items specified in the list. The format of the list file comprises a type designation followed by one or multiple spaces and then the non-equivalence point.

inst yak_zcvg_inst/skip_pix_reg port te_coord[5] inst yak_hah_inst/x_start_pa_reg_31_ inst yak_hah_inst/x_end_pa_reg_30_ inst yak_hah_inst/x_end_pa_reg_29_ inst yak_hah_inst/x_end_pa_reg_28_ inst yak_hah_inst/x_end_pa_reg_27_ inst yak_hah_inst/x_end_pa_reg_26_ pin yak_hah_inst/u_sync_cell/D

The ECO list file is incorporated using the '-list_file' option within the 'read_design' command. It can be generated from a Third Party LEC non-equivalence result file. For instance, in Synopsys Formality, the command 'report_failing_points > formality_non_eq.report' generates such a file. In a GOF ECO script, this report file is then read in and converted into the list file.

Below is an example script demonstrating the conversion of Third Party LEC results and execution of GOF ECO with the 'list_file' option:

use strict; my $list_cont = ""; open(FIN, "formality_non_eq.report"); while(<FIN>){ if(m/Ref\s+(\w+)\s+r:\/\w+\/\w+\/(.+)/){ my $fm_type = $1; my $point = $2; my $gof_type = "inst"; if($fm_type =~ m/Pin/){ $gof_type = "pin"; }elsif($fm_type =~ m/Port/){ $gof_type = "port"; }else{ # For instance type $point =~ s/\[/_/g; # Mostly abc_reg[0] has name changed to abc_reg_0_ in the netlist $point =~ s/\]/_/g; } $list_cont .= "$gof_type $point\n"; } } close(FIN); open(FOUT, ">eco_list.txt"); print FOUT $list_cont; setup_eco("eco_list_file"); # Setup ECO name set_log_file("eco_list_file.log"); read_library("tsmc.5nm.lib");# Read in standard library read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("SOC_TOP"); set_pin_constant("test_mode", 0); set_pin_constant("scan_en", 0); set_ignore_output("test_so*"); fix_design("-list_file", "eco_list.txt"); # -list_file option to read in the ECO list file with the ECO points report_eco(); write_verilog("eco_verilog.v"); exit;

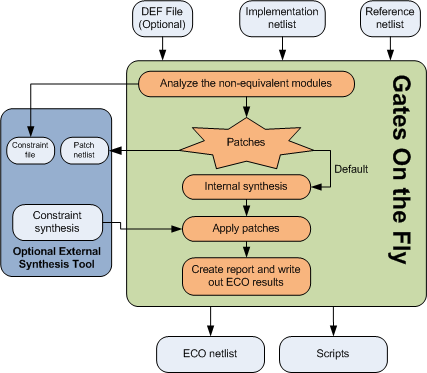

In Metal Only ECO, the design has completed place and route. Any new gates added should map to spare gates that located in the design. GOF supports Standard Spare Cells and Metal Configurable Gate Array Spare Cells post-mask metal only ECO.

Figure 17: Metal Only ECO

In metal only ECO, the primary objective is to fix the logic without altering the base layers, thus avoiding costly and time-consuming changes to the silicon. The process involves two main steps: fixing the logic and mapping new gates to spare type gates. This article focuses on the second step, detailing how spare gates are utilized in metal only ECO and the intricacies involved in standard cells spare gates mapping.

1. Fix Logic Automatically: The initial step is to automatically correct the logic in the design. This involves identifying the required changes and determining how these changes impact the existing netlist.

2. Map New Gates to Spare Type Gates: The subsequent step is to map all new gates to the existing spare gates. This requires a specialized synthesis process to create a new netlist patch that exclusively uses gate types available in the spare gate list. Special attention is needed for flip-flop (flop) mapping to ensure compatibility.

GOF ECO employs an internal synthesis engine to map the patch logic onto spare gates. The spare gates should comprise specific combinations to ensure optimal area and performance. The primary combinations are:

Among these, the second combination (two ports 'nand/nor' gates, 'inv' gates, and flops) offers the least area, while the third combination (two ports 'nand/nor/and/or' gates, 'inv' gates, and flops) provides the best performance in metal only ECO scenarios.

In the mapping process, as illustrated in Figure 18, gates such as MUX and flops are mapped directly onto the spare gates due to their one-to-one correspondence with the spare gate list. However, more complex cell types like AO32 require synthesis and mapping onto multiple simpler gates. For example, an AO32 gate might be synthesized and mapped onto three AND gates and one NOR gate.

Figure 18: Standard Cells Spare Gates Mapping

A common challenge in metal only ECO is when the new flop required has a different set/reset type compared to the available spare flops. For instance, an ECO may necessitate a set-type flop, but the spare flop list might only provide a reset-type flop. In such cases, GOF ECO uses a phase invert technique to map the set flop to the available reset spare flop, ensuring functionality is preserved.

Figure 19: Map new set-type flop to spare reset-type flop in metal only ECO

Metal only ECO is a critical process in ensuring the efficient and cost-effective implementation of design changes. By leveraging spare gates and utilizing specialized synthesis techniques, it is possible to map new logic onto existing spare gates, thereby avoiding the need for more extensive silicon modifications. Understanding the combinations of spare gates and the mapping process is essential for optimizing area and performance in metal only ECO.

GOF ECO utilizes a heuristic method that employs constraints to identify the optimal mapping of spare gates. The process involves setting constraints to restrict the types of NAND/NOR/AND/OR gates to be considered, and then conducting a mapping exercise to identify the nearest available spare gates. The cost of the mapping is determined by adding the distance between the measured location and the actual location of the spare gate. For example, if a NAND gate needs to be mapped in a metal only ECO, and the measured location is (100, 100), while the closest spare gate (spare_0) is located at (120, 120), then the cost is calculated as (120-100)+(120-100)=40. The method involves multiple iterations, and the optimal solution is selected based on the lowest cost.

To ensure that new instances are accurately mapped to the nearest spare gate instances, it is necessary to have a Design Exchange Format (DEF) file. Without loading the DEF file, the GOF process will use spare gate types without precise mapping to exact spare instances. However, P&R tools like SOC Encounter will map new instances in the new netlist to the closest spare gates.

During the 'fix_design' command, GOF examines the top-level module and its sub-modules to identify any non-equivalent points and optimize the logic cone to create a patch circuit with the minimum number of gates.

Spare gates are incorporated into the design and their percentage relative to the entire digital area is usually dependent on the design maturity. For instance, the first version of a design typically requires a higher percentage of spare cells, usually around 8-10% of the entire digital area. As the design progresses to the second version, a lower percentage of spare cells, approximately 4-5% of the total digital area, is sufficient. By the third version, less than 3% additional spare cells may be necessary. Additionally, during the backend placement process, any remaining empty space can be filled with extra spare gates.

Besides the spare gate area percentage, the proportion of various spare gate types is also crucial. For example, a design with 126K instances may have spare gates in different categories, as depicted in the following figure:

Figure 20: Spare Gates numbers and distribution

Usually, spare gates are uniformly distributed on the floor plan, as shown in figure 20. Nevertheless, if accessible, users can adjust the distribution based on historical metal only ECO data. Blocks that are prone to design changes may require more spare gates, while mature logic may require fewer spare gates.

A typical process for an automatic Metal Only ECO:

GOF script has the exact same syntax of Perl script. It runs the exported commands that access the netlist database and modify the netlist.

The following shows an example of an automatic Metal Only ECO:

The script can be run by '-run' option.

gof -run run_metal_only_example.pl

User can insert 'die' command to let GOF stop in some point and do interactive debugs when ‘GOF >' shell appears. GUI mode can be enabled by run 'start_gui' command.

Check Run and debug GOF script section for more detail

If the automatic metal only ECO has new gated clock cells added while the spare gates list doesn't have gated clock cell, "convert_gated_clocks" API should be run to convert gated clock cells to 'MUX' type logic. GOF maps the 'MUX' type logic to the spare type gates in 'map_spare_cells' API.

Metal configurable gate array cells are specially developed for Metal Only ECO. These cells come in two types, which are used in different backend stages. The first type is gate array spare cells, which are typical filler or decap cells used in the original flow. During the backend P&R stage, gate array spare cells such as GFILL/GDCAP are incorporated and distributed throughout the design. The second type is gate array functional cells, which are used in post-mask ECO. Gate array spare cells are replaced with gate array functional cells such as GAN2, GND2, and GXOR2.

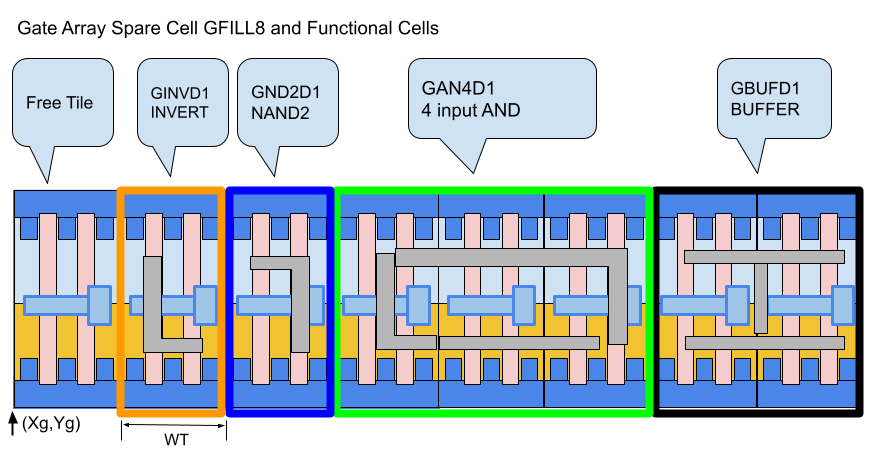

The base unit of gate array cell is a tile. Every gate array cell consists of one or more tiles. Use one 5nm standard library as example:

| Tile Numbers | Spare Cells | Functional Cells |

|---|---|---|

| 1 | GFILL1 | GTIE GINVD1 GND2D1 GNR2D1 |

| 2 | GFILL2 | GBUFD1 GAN2D1 GOR2D1 GAOI21D1 GDN3D1 |

| 3 | GFILL3 | GAO21D1 GAN4D1 GOR4D1 |

| 4 | GFILL4 | GINVD8 GAN2D4 |

| 5 | GFILL5 | GMUX2D1 GXOR2D1 GXNOR2D1 |

| 6 | GFILL6 | GBUFD8 GSDFFRQD1 GSDFFSQD1 |

| 8 | GFILL8 | GINVD16 |

| 12 | GFILL12 | GCKLNQD6 |

Table: Tile Numbers in Gate Array Spare Cells and Functional Cells

Gate array cells have a larger size than normal standard cells. For instance, GFILL1 is four times larger than FILL1, and GND2D1 is 25% larger than ND2D1. However, the power consumption and timing of these cells are similar.

Each gate array spare cell has a location defined by a DEF file. In Figure 21, the location of one GFILL8 spare cell is defined as (Xg, Yg), with a tile height equivalent to that of GFILL1 and a tile width eight times that of GFILL1.

GFILL8 tiles can be regrouped and rewired in metal layers to create different functional cells. For example, GBUFD1 requires two tiles and implements a buffer function, while GAN4D1 uses three tiles to create a 4-input AND function.

Figure 21: Gate Array Spare Cell GFILL8 Regrouped Tiles to Form Functional Cells

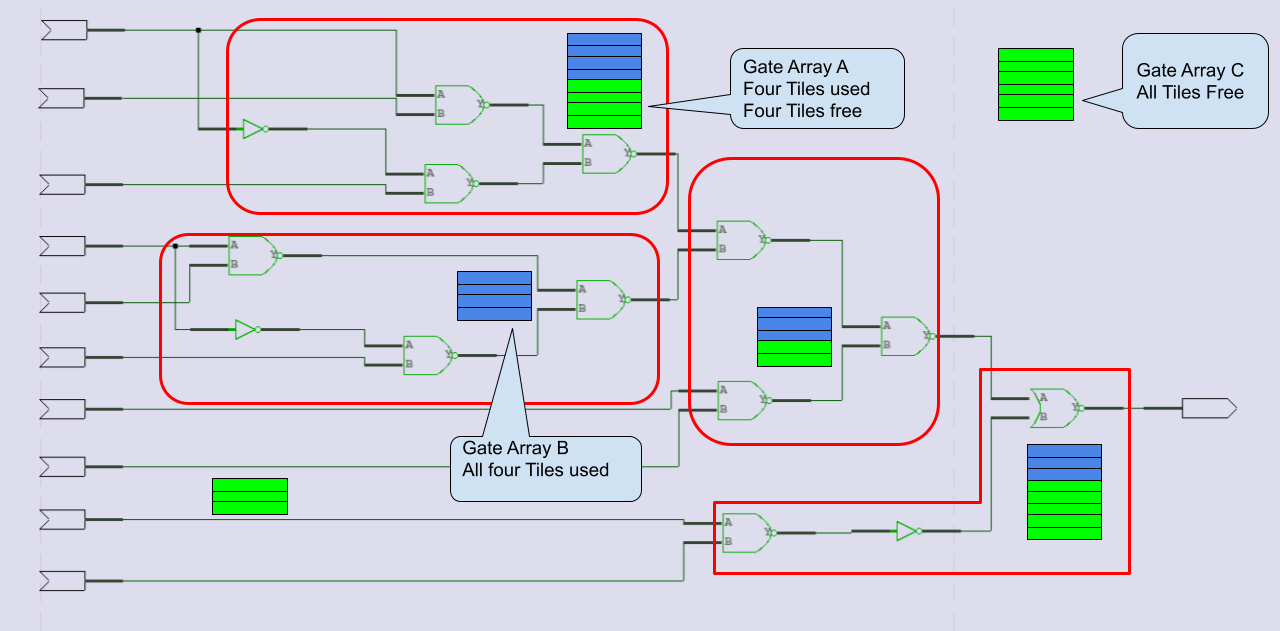

When generating a patch, GOF synthesizes it using only gate array functional cell types. These functional cells are then mapped to the most optimal nearby gate array spare cells with the minimum wire connection costs.

Figure 22: Gate Array Spare Cells Mapping to Functional Cells

Once the mapping and swapping process is complete, some gate array spare cells may have portions of their tiles being used by several functional cells, as shown in Figure 22. To properly save the ECO results, the type of these gate array spare cells should be changed. For instance, gate array A should have its type changed from GFILL8 to GFILL4. Any completely used up gate array spare cells, such as gate array B with type GFILL4 and all four tiles being used, should be deleted.

The mapped gate array functional cells need to be moved to the locations of their corresponding gate array spare cells, with the horizontal location X adjusted based on the starting tile location. For example, the GINVD1 instance should be moved to (Xg+TW, Yg), and the GBUFFD1 instance should be moved to (Xg+TW*6, Yg), as shown in Figure 21.

GOF writes out an ECO verilog file and backend tools ECO scripts. In the verilog file, the location of the newly added gate array functional cells is written in comments. GOF supports both Synopsys ICC script and Cadence Encounter script, both of which have cell location placement support.

For example, when saving the result in an ICC TCL script, the cells in Figure 21 would have the following commands:

Encounter script format:

Note:Tile size assumed to be 0.20 X 0.22; GFILL8 location (Xg, Yg)=(253.82, 413.28)

A typical process for gate array spare cells ECO:

GOF script has the exact same syntax of Perl script. It runs the exported commands that access the netlist database and modify the netlist.

The script can be run by '-run' option.

gof -run run_gate_array_cells_eco_example.pl

User can insert 'die' command to let GOF stop in some point and do interactive debugs when "GOF > " shell appears. GUI mode can be enabled by run 'start_gui' command.

Check Run and debug GOF script section for more detail

For certain ECO cases, specifically those involving changes to combinational signals, manual ECOs may prove to be quicker and more effective. However, identifying equivalent wires in the netlist for RTL signals can be a challenging aspect of such manual ECOs. This is primarily due to the fact that combinational signals are often optimized during synthesis. To help alleviate this issue, GOF offers an API called 'find_equal_nets' as well as GUI operations to assist in the search for equivalent nets in the netlist for RTL signals.

The following is the example script for finding equal nets in netlist for RTL:

# GOF script, find_equal_nets.pl use strict; read_library("art.5nm.lib");# Read in standard library set_define("SYNTHESIS"); set_define("NO_SIM"); set_inc_dirs("/project/nd900/vlib/include", "/project/nd900/IPS/include"); read_rtl('-ref', "ref0.sv", "ref1.sv", "ref2.sv"); read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-imp", "implementation.gv");# Read in Implementation Netlist set_top("topmod");# Set the top module elab_rtl; find_equal_nets("row_full", "sync_start"); # Find row_full and sync_start in the netlist

Please refer to 'Find Equal Nets in Netlist Window' for the detail

In many cases, the ECO operations are well known by users. They can be inserting buffers to a 128bits bus, or adding isolation AND gates to all outputs of a module. In these cases, manual ECO by scripts is more efficient and resource saving.

GOF exports many APIs for ECO operations in GOF script.

A typical situation for a Manual ECO:

These APIs change Implementation Netlist

For the full list of the APIs, user can type 'help' in 'GOF >' shell.

For the individual API, type 'help api_name' . For example:

Check Run and debug GOF script section for more detail

A Perl 'for' or 'foreach' loop can handle repetitive work efficiently. For example, to add a 'AND' isolation gate for every output port of a module.

The special character '-' is used to represent existing connection. For example

A buffer is inserted into A pin of instance U0. The old existing net drives the new buffer now.

The special character '.' is used in ECO new instance name if the new instance needs to be in the same hierarchy as the ECO spot.

If the instance is empty, GOF creates 'AOI21X2' in the current top level. With ".", GOF creates 'AOI21X2' new instance in hierarchy "u_qcif/u_num2/u_spare1".

In Manual Metal Only ECO, any new added gates are automatically mapped to spare gate instances by 'map_spare_cells' command. A Design Exchange Format file has to be loaded for the tool to find optimal spare instances. If the file is not present, the mapping is skipped.

The script can be run by ‘-run' option.

gof -run manual_metal_eco.pl

Check Run and debug GOF script section for more detail

The following paragraph demonstrates how to insert buffers and inverters into a circuit in GUI mode.

Start up GOF by the command line

For detail usage, visit this link

https://nandigits.co/usage.htm

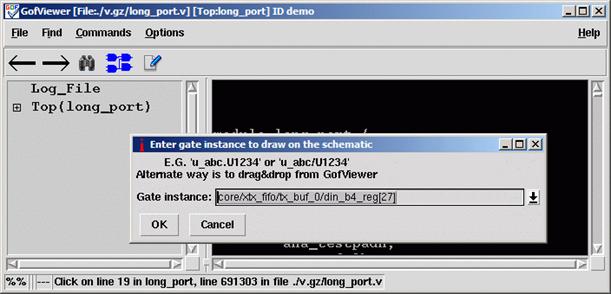

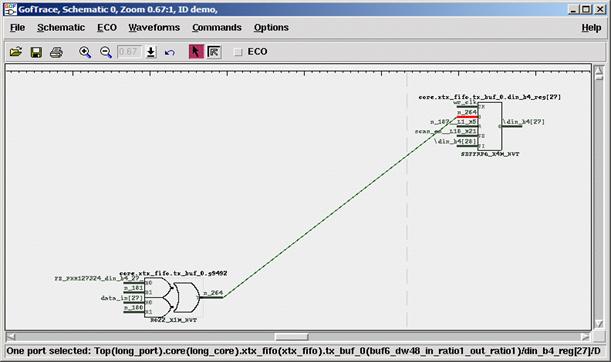

In GofViewer netlist window, press ctrl-g or menu commands->'Launch GofTrace with gate'. Fill in the instance name that needs ECO.

Figure 23: Load gate to schematic

In GofTrace schematic window, use mouse middle button to expand the schematic. In this case, pin D of the flop should be inserted an invert.

Figure 24: Partial Schematic for GUI ECO

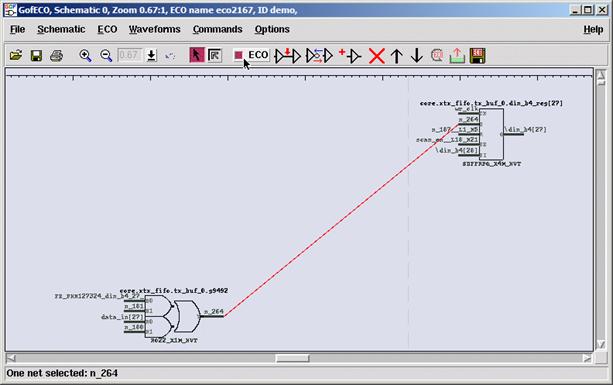

Check ECO button to enable ECO mode

Figure 25: Schematic in ECO Mode

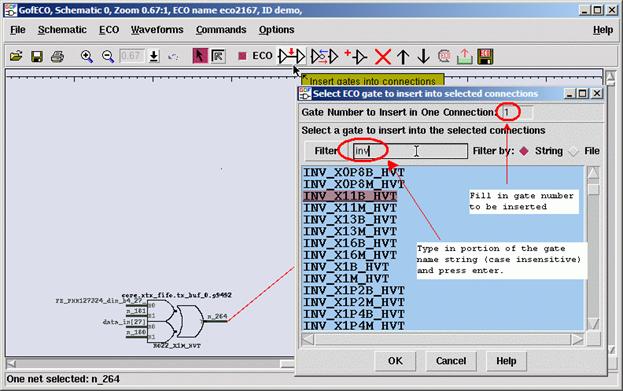

Press mouse-left-button on the wire to select it. Click ECO button ‘Insert gates into connections', select the right invert in the gate type selection window.

Figure 26: Select Gate in GUI ECO

In ‘Pin Connections' setup window, use default ‘Complete Loop' option, so that the gate can be inserted in the net.

Figure 27: New Cell Pin Connection Selections

Click OK and the invert is inserted.

Figure 28: Manual ECO with New Gate Inserted

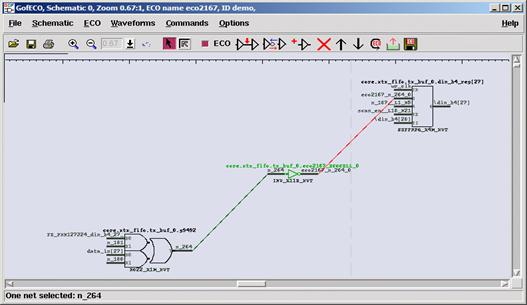

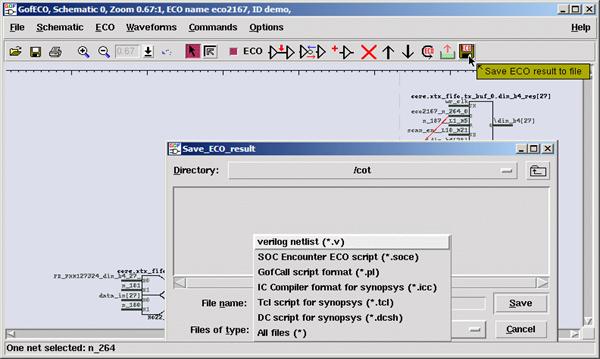

Press ECO button ‘Save ECO result to file'. And select the format to be saved. The supported formats include verilog netlist, SOC Encounter ECO script, GOF script, TCL script and DCShell script.

Figure 29: Save ECO in GUI Mode

Metal ECO can only use existing spare gates on the silicon. GOF controls how to use these spare gates.

Four methods are supported in Metal Only ECO:

Note: 'Spare type gate' refers to the gate type, 'INVX2', 'NAND2X2'. 'Exact spare gate instance' refers to the spare instances in the design, E.G. 'spare1/spare_invx2'

The detail setup for four method can be found in GOF ECO Metal Only ECO. Use cases can be found in online document.

Timing can be reported before or after ECO by report_timing API.

Timing report related APIs are these:

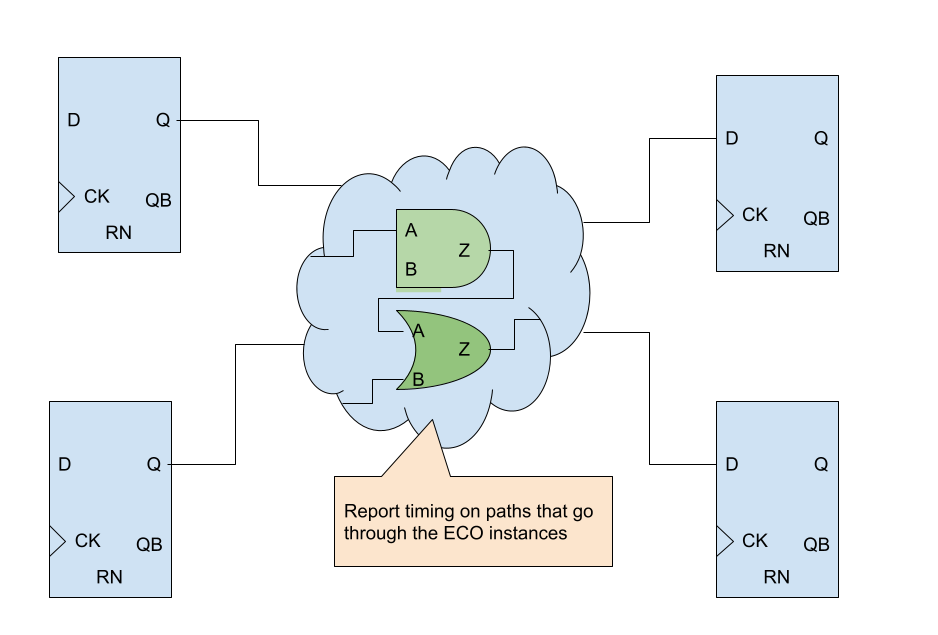

In order to report the timing in paths of interest before a functional ECO, it is necessary to specify the option of 'from,' 'to,' or 'through' in the report_timing function. By comparing the numbers obtained before and after a functional ECO, an appropriate timing ECO method can be selected.

After performing a functional ECO, report_timing can utilize the 'from,' 'to,' or 'through' options. If the function is executed without specifying any of these options, it will report the timing of paths that traverse the ECO instances.

Figure 30: Report timing on paths through ECO instances

GOF Formal is one of the function components integrated in GOF platform. It provides a formal method to calculate fault coverage in an IC design in functional safety.

ISO26262 defines functional safety as "the absence of unreasonable risk due to hazards caused by malfunctioning behavior of electrical and electronic systems". Four ASILs are proposed to represent four degrees of automotive hazards. In IC component, the coverage in the ASIL requirement is the fault coverage in the logic circuit. Specifically, single point fault metric (SPFM) and latent fault metric (LFM) should meet minimum numbers for the corresponding ASIL levels. The following table lists the three ASIL levels with specific coverage numbers defined in the standard.

| ASIL | SPFM | LFM |

|---|---|---|

| B | ≥90% | ≥60% |

| C | ≥97% | ≥80% |

| D | ≥99% | ≥90% |

The traditional method to calculate the fault coverage is pure simulation based. It's inefficient and time consuming. GOF Formal provides a formal and efficient way to calculate the SPFM and LFM numbers of a logic design. It can work in a standalone mode to calculate the coverage metric. And it can also work as a supplemental method to cover the faults left over from simulation based process.

Single point fault (SPF) is the fault in the IC design that leads directly to the violation of a safety goal which is defined as observation point in the "Cone of Influence" section below and no fault in the IC circuit is covered by any safety mechanism. However, if there is safety mechanism, but the fault can't be covered by the safety mechanism, the fault is called residual fault according to the standard. In calculating SPFM, residual fault is treated as single point fault. Latent faults are multiple-point faults not detected by a safety mechanism or perceived by the driver. The latent fault metric is to determine whether coverage by safety mechanisms is sufficient to protect against risk from latent faults in the IC design.

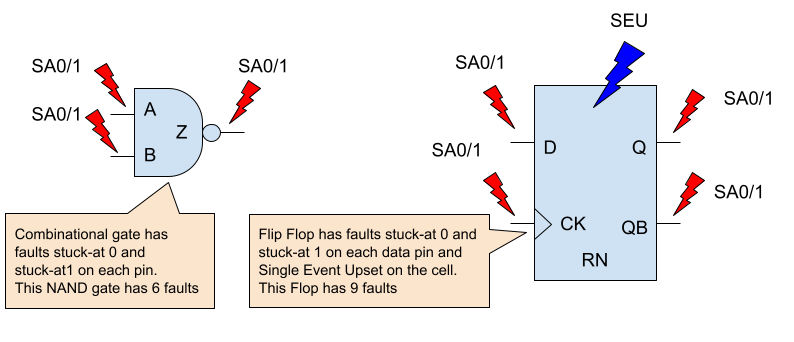

GOF Formal injects faults to each input port and each pin of logic gates. Each input port has stuck-at 0 and stuck-at 1 faults injected. Every combinational gate has stuck-at 0 and stuck-at 1 faults injected into each pin. For flip-flop, stuck-at 0 and stuck-at 1 faults are injected into each data and clock pin. And flip-flop has Single Event Upset (SEU) fault injected to the state in random time.

Figure 31: Fault model for logic gates

SPFM and LFM metrics can be calculated in two methods, rough mode and detail mode. The rough mode is done by structural analysis of the Cone of Influence. The detail mode is calculated by formal analysis of the Cone of Influence.

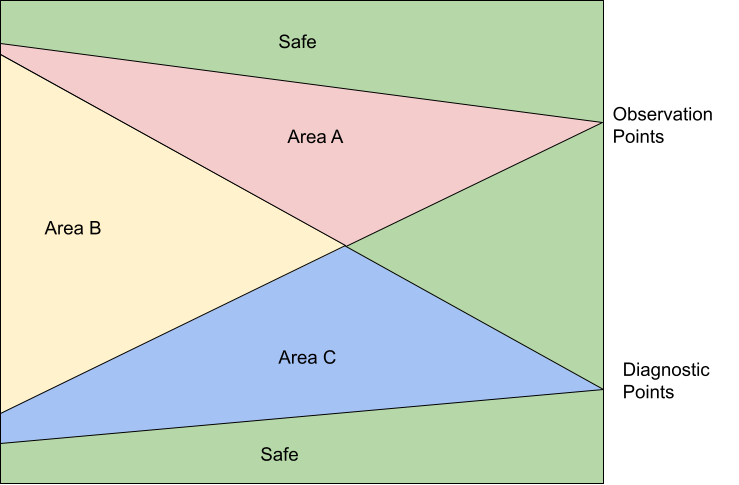

Two types of strobing points shall be defined for the Cone of Influence extraction.

The observation points are the outputs or registers that are impacted by the injected faults which affect functional safety and violate safety goal. The diagnostic points are the outputs or registers to check if injected faults can be detected at these strobing points or perceived by the up level driver.

The logic back traced starting from the observation points and the diagnostic points all the way to the inputs or black boxes. The Cone of Influence (COI) is created for the observation points and the diagnostic points respectively. Each cell and each input port in the cones will be injected faults according to the Fault Model section.

Figure 32: Cone of Influence

In Figure 32, all faults that are outside of the two COIs are safe faults.

Area A has faults that are observable but not detectable, so they can be classified as residual faults. And they are called single point faults if safety mechanism is not implemented for the design, in which case the diagnostic points are not present and Area B and Area C are zero size. However, if they don't propagate to the observation points in the detail formal COI analysis, they can be classified as multiple point faults. For example, TMR is implemented on Area A. The majority faults in this area will become multiple point faults.

Area B has faults that are classified as multiple point faults, since they are observable and detectable. In the rough structural COI analysis, the worst SPFM metric can be calculated by assuming them as all residual faults and the best SPFM metric by assuming them as propagatable to the diagnostic points. So the detail formal COI analysis will determined the fault classification.

Area C has faults that are classified as detectable multiple point faults, but they are not observable. The detail formal COI analysis will be run on Area C to check if the faults in this area can not propagate to the diagnostic points, then they can be classified officially as latent faults. The best and worst LFM metrics can be gained by the rough structural COI analysis method.

The Single Point Fault Metric (SPFM) can be calculated according to the following equation.

SPFM = 1 - Σ(λSPF+λRF)/Σ(λ)

where:

λSPF: Single Point Fault when there is no safety mechanism

λRF: Residual Fault

λ: Any Fault

The Latent Fault Metric (LFM) can be calculated according to the following equation.

LFM = 1 - Σ(λMPF_UD)/Σ(λMPF - λSPF - λRF)

where:

λMPF_UD: Multiple Point Fault not detected by the driver

λMPF: Any Multiple Point Fault

λSPF: Single Point Fault when there is no safety mechanism

λRF: Residual Fault

In the rough method calculation by analyzing COI structure, the best and worst metrics can be quickly calculated.

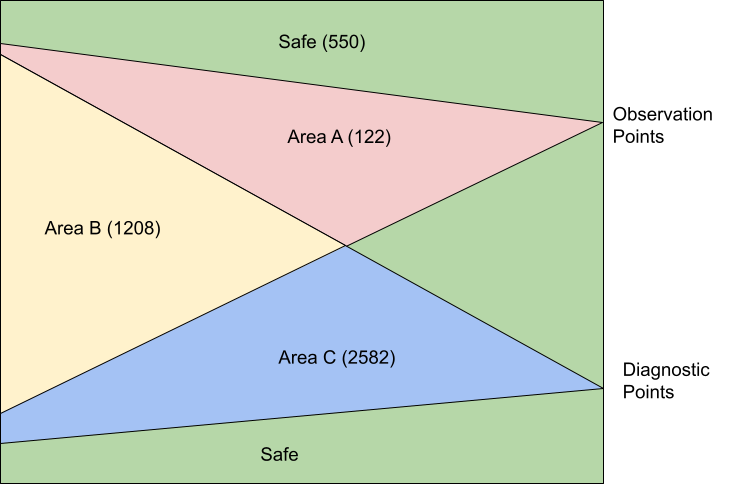

In the example shown in Figure 33, the faults are distributed as:

The best SPFM assumes the faults in Area B are propagatable to the diagnostic points. The single-point/residual faults Σ(λSPF+λRF) has number 122 only in Area A. Therefore, the best case SPFM is 97.3%.

The worst SPFM assumes the faults in Area B are all residual faults, so Σ(λSPF+λRF) has number 1330 which is 1208 plus 122, and get calculated metric to be 70%.

The best LFM assumes the faults in Area C are all detectable. Σ(λMPF_UD) is zero, So LFM is 100% in the rough structural COI analysis.

The worst LFM assumes the faults in Area C can not propagate to the diagnostic points, and they are not detectable. Therefore, Σ(λMPF_UD) has the number of 2582, and the worst LFM is 59.5%.

Figure 33: Example fault numbers in COI

The formal COI analysis needs to be run to get the final accurate metrics. For each fault injected, GOF Formal either proves that a path exists to propagate the fault to the observation or diagnostic points, or disprove there is such path. A path means by toggling input ports in some limited clock cycles, the fault can propagate to the observation/diagnostic points.

GOF Formal doesn't require stimulus nor is a testbench required. The tool automatically determines the stimulus. For each fault injected, two designs are compared to see if the specified outputs are equal. One design is the fault injected design, the other is the original design. The specified outputs are the observation points or the diagnostic points set by user. The faults to be injects can be thousands or millions. GOF Formal uses cluster command to fully utilize the cluster computing power. Thousands of jobs can be submitted in parallel to the cluster machines with only one license being used.

After the detail formal COI analysis of the above example, the residual fault number is 178, and the final SPFM is 96%. The latent fault number is 260, so the final LFM is 94%.

In order to improve the fault coverage, safety mechanisms should be built in the IC design. There are several approaches for safety mechanism implementation.

In Figure 33, a safety mechanism can be a double modular design or ECC design. The diagnostic points would be the alarm bits in the double modular error bit, or ECC error recovering signals. For SPFM metric improvement, those gates in Area A that are not covered by safety mechanism can be modified to support TMR (Triple Module Redundancy), so that λSPF can be further reduced and SPFM improved accordingly. See this TMR ECO Case

One example script for SPFM and LFM calculation:

set_log_file("spfm_lfm.log"); # Set log file name read_library("art.5nm.lib"); # Read in liberty file read_design('-imp', 'ecc_process.v'); # Read in the design block set_top("ecc_top"); # Set the top module name create_clock("data_clk", 2); set_pin_constant("test_mode", 0); # Set pin constraint set_observe_points("data_out*"); # data_out[31:0] affects functional safety set_observe_points("synd_out"); # synd_out affects functional safety set_detect_points("sb_err_o"); # Safety mechanism detecting output set_detect_points("db_err_o"); # Safety mechanism detecting output verify_faults("-full"); # Calculate and print SPFM and LFM, Use verify_faults("-coi") for fast SPFM/LFM calculation gexit;

The API verify_faults can run on an individual fault to check if the fault can propagate to the observation points. If the fault is observable, a VCD file can be dumped to show how to toggle the input ports cycle by cycle to propagate the fault. All internal signals waveforms are captured in the VCD file.

The following script is to check if one SEU fault can propagate. If yes, a VCD file is dumped:

set_log_file("spfm_lfm.log"); # Set log file name read_library("art.5nm.lib"); # Read in liberty file read_design('-imp', 'ecc_process.v'); # Read in the design block set_top("ecc_top"); # Set the top module name set_pin_constant("test_mode", 0); # Set pin constraint set_observe_points("data_out*"); # data_out[31:0] affects functional safety set_observe_points("synd_out"); # synd_out affects functional safety # To check if the fault can be propagated to the detect points, set_observe_points on the detect points verify_faults("u_ecc_ops/bit_reg:SEU", "-vcd", "debug_seu.vcd"); # Check if the Single Event Upset on the flop can propagate gexit;

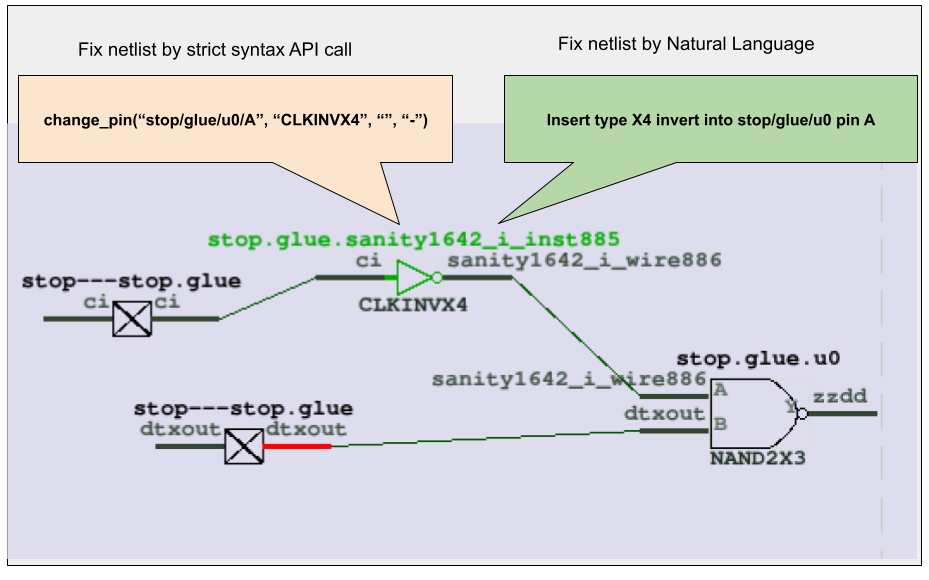

The GOF Script Interface can access and modify the internal netlist design database through exported APIs. When the AI Client is activated, users can describe ECO changes in natural language. GOF then translates these descriptions into internal API calls to implement the netlist modifications.

One key element to do efficient manual ECO is to isolate the ECO spots quickly. The following APIs are for fast Netlist Browsing.

For example, to get data pins of flops in one module. The script can use these browse APIs

After run the script, @flop_data_pins have all data pins of all flops in the module.

These APIs are for Automatic ECO

These APIs are for reading/writing files.

These are APIs for Manual ECO.

Combining netlist browsing APIs, a short GOF script can do very efficient ECOs.

For example, to add isolation cells for all output ports of a module.

These APIs are for Automatic ECO

For detail of APIs visit Appendix A

Any string in GOF script for module/instance/wire/pin/port should be enclosed by single quote or double quote. When a Perl variable is used, double quote should be used

Instance with backslash should be either put in single quote and with a space in the end.

Net name with backslash should keep the backslash and space. For example

The net '\u_abc/u_def/net123 ' should have backslash and space kept in API, for example:

In Linux Shell, the script can be run by ‘-run' option.

gof -run run_example.pl

If '-run' option is present in the command line, and 'exit' or 'gexit' is not in the script, or GOF meets error when executing the script, GOF goes into interactive mode with GOF shell 'GOF >'.

Individual command can be executed in GOF shell. The command can be in nested mode

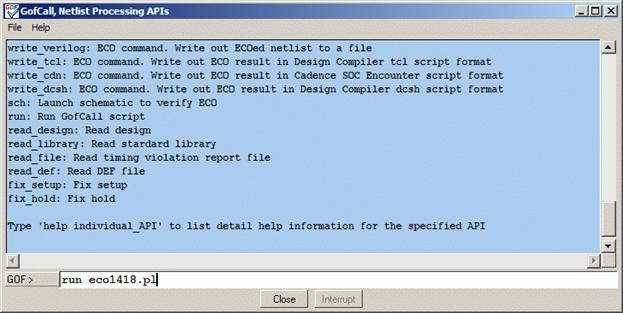

GOF scripts can be run in GUI window. In GofViewer, click Menu Commands->'Launch GOF Script Interface' to launch GOF GUI window.

Type ‘help' in the shell entry for help information. Scripts can be run by '-run' command in the shell entry

Figure 34: GofCall window

In GOF shell, GUI windows can be launched by 'start_gui' or 'sch' commands.

'start_gui' launches netlist view window first and user can bring up schematic window from netlist view window.

'sch' command only launches schematic window, and it doesn't enable netlist view window. So it has fast turnaround in GUI interactive debug.

For example,

After the following command is done,

Run 'sch' in 'GOF >'

The instance is loaded into a schematic and user can click on the instance's pins to trace fanin/fanout on the schematic to see if the ECO is done as expected.

'sch' fast schematic launch command can be used as break points for debug. For example, 'sch' commands are inserted in GOF script, when the tool runs to the point, a schematic is launched.

On the schematic, user can use mouse-middle-button clicking on the pin 'D' to see if the ECO is done as expected.

Figure 35: Launch schematic at break point

Note: 'ECO' check-button is enabled automatically, since there is ECO having been done.

To compare with the logic before ECO, launch a new schematic by menu Schematic->'New Schematic'. On the new schematic, press 'ctrl-g' or by menu Schematic->'Load Gate' to load in the flop under ECO.

Figure 36: Launch schematic before ECO

Note: 'ECO' check-button is un-checked.

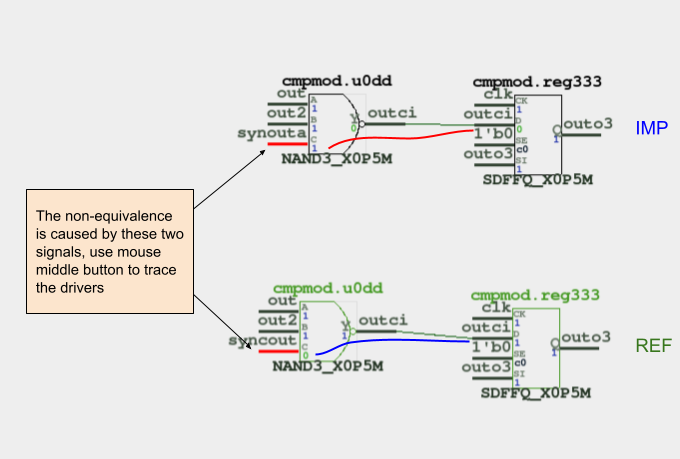

In GOF shell 'GOF > sch the_non_equivalent_point -both', so that both instances/ports in the Implementation and Reference Netlists are loaded into a schematic. Select both of them, right the mouse and select 'LEC Debug the_non_equivalent_point'. After the run finishes, use mouse middle button to expand the schematic, and the counter-example values are back-annotated on the schematic.

Figure 37: Debug non-equivalence by counter-example back-annotated

Two corresponding flops, two corresponding output ports, and any two nets in the Reference Netlist and the Implementation Netlist can be compared in debug mode. In cases where the outcome is non-equivalent, the counterexample will be presented to the gate pins on the schematic.

Figure 38: Counter-example back-annotated on the schematic

Both input port and output port have the same operation

Powered by AI, GOF brings Natural Language ECO operations to life, allowing users to skip complex API manuals. Instead, they can simply describe the required ECO modifications in plain English, detailing where new logic should be inserted and which gates to create and connect. Natural Language input is clearly more user-friendly and intuitive. Since this input is translated into detailed API calls, the debugging process remains robust. Additionally, the GOF Debug GUI interface streamlines debugging, making it highly convenient. As shown in Figure 39, Natural Language descriptions simplify the user experience significantly.

Figure 39: Use Natural Language to fix netlist

Example script for Natural Language ECO operations:

# AI powered Natural Language ECO operations use strict; # To catch script syntax issue # Setup ECO name 'auto_svf' setup_eco("auto_svf_example"); read_library("/lib/5nm/tsmc_typ_85c_078v_svt.lib"); # Read in standard library read_design("-imp", "/proj/ai_acc/post/implementation.gv"); # Read in Implementation Netlist file Which is under ECO set_top("topmod"); set_ai(1); # Enable AI run_nl("Insert type X4 invert into stop/glue/u0 pin A"); # NL ECO run_nl("Change pin B of stop/glue/u0 to fun_clk"); run_nl("Insert a NAND into stop/glue/regsame/D pin, insert a MUX into B pin of the NAND, connect the MUX S0 pin to net bi, connect the Mux B pin to a new inserted AND gate, the AND gate is driven by net dft_clk and pin mmux0/du0/Y, connect the MUX A pin to net ci"); write_verilog("eco.gv");

If the AI Server is not installed, the AI Tech Support on NanDigits Website can be used to convert the Natural Language description to ECO script.

The plain language in the third run_nl command above can be converted by the AI Tech Support into a Perl ECO script:

$inst_arr_nand = do_auto_change("action=insert_gate", "instance_pin=stop/glue/regsame/D", "gate_type=nand"); $inst_nand = $inst_arr_nand->[0]; $inst_arr_mux = do_auto_change("action=insert_gate", "instance_pin=$inst_nand/B", "gate_type=mux"); $inst_mux = $inst_arr_mux->[0]; do_auto_change("action=change_pin", "instance_pin=$inst_mux/S0", "connections=bi"); $inst_arr_and = do_auto_change("action=insert_gate", "instance_pin=$inst_mux/B", "gate_type=and2", "connections=dft_clk,mmux0/du0/Y"); do_auto_change("action=change_pin", "instance_pin=$inst_mux/A", "connections=ci");

The AI Tech Support is accessible at https://nandigits.co/askbot.php. Users can copy the generated Perl ECO script into their full ECO script as a workaround if the AI Server not installed.

The GOF platform features a built-in powerful logic equivalence checker tool called GOF LEC. While not mandatory, the tool can benefit from SVF files in certain cases. It is strongly advised to utilize SVF files if they are obtainable, especially for designs with multibit flop. The two designs being compared can either be in RTL or Netlist format, with RTL supporting SystemVerilog2017. The read design method differs depending on whether RTL or Netlist is being supported.

Figure 40: GOF LEC Engine

The following is the example script for Netlist to Netlist LEC:

# LEC script, run_net2net_lec.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_svf('-ref', 'AI2023_top_syn.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_svf('-imp', 'AI2023_top_pr.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_design('-ref', 'AI2023_top_syn.v'); # Read in the Reference Netlist, prelayout netlist read_design('-imp', 'AI2023_top_pr.v'); # Read in the Implementation Netlist, postlayout netlist set_top("AI2021_top"); # Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); my $non_equal = run_lec; # Run logic equivalence check on the two netlists if($non_equal){ gprint("LEC failed with $non_equal non-equivalent points"); }else{ gprint("LEC passed"); }

The following is the example script for RTL to Netlist LEC:

# LEC script, run_rtl2net_lec.pl use strict; read_library("art.5nm.lib"); # Read in standard library set_inc_dirs("-ref", "inc_dir_path/include"); set_define("-ref", "NO_SIMULATION", 1); my @rtl_files = ("cpu_core.sv", "mem_ctrl.sv", "display_sys.sv", "chip_top.sv"); read_rtl("-ref", @rtl_files); # Read in the Reference RTL files read_svf('-imp', 'chip_top.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_design('-imp', 'chip_top.v'); # Read in the Synthesis Netlist set_top("CHIP_TOP"); # Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); elab_rtl(); # RTL processing my $non_equal = run_lec; # Run logic equivalence checking on RTL vs Netlist if($non_equal){ gprint("LEC failed with $non_equal non-equivalent points"); }else{ gprint("LEC passed"); }

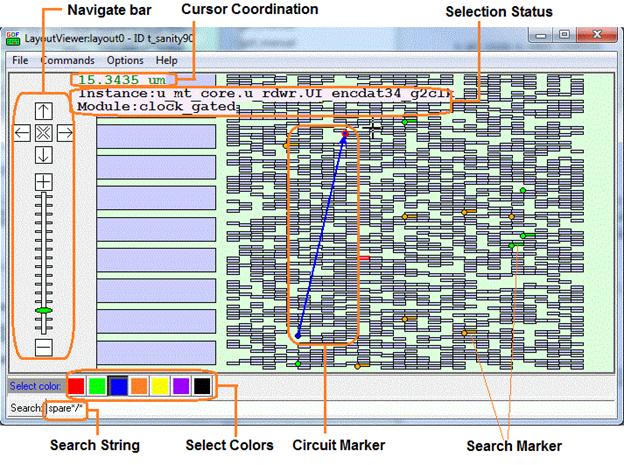

GOF Debug has been spun off into an independent tool, offering users the flexibility to purchase licenses on a daily basis. For more information on licensing options, please refer to the Purchase page.

GOF Debug encompasses a comprehensive debugging process, including:

This chapter will delve into the details of GUI operation, providing a thorough understanding of its features and applications.

When GOF is run without '-run' or '-shell' option, it goes into GUI mode.

gof -lib t65nm.lib -lib io.liblong_port.v

GofViewer is the first window after GOF starts up GUI interface.

Figure 41: GofViewer Window

If there errors or warnings in loading the database, Log Window pops up

Figure 42: Log Window

Users can input netlist files and design files through the Load Design command.

If any netlist file or design file has been updated during GOF session, this command can be used to reload the design.

This command loads another netlist file to create a new hierarchical tree. The hierarchy tree is listed in the hierarchy list window. The command is useful when users want to draw circuits from different netlist file on the same schematic which is good for logic comparison in netlist debug scenario such as LEC failures analysis.

The command opens log file in a text window.

Exit command.

This command searches for the matching string in the netlist text window.

GOF loads only one module in the netlist text window when the netlist file is hierarchical with multiple modules. The command loads the corresponding module into the text window and highlight the line with the specific number in the netlist file.

This command reports the design area. The command requires standard library files to be loaded which include leaf cell area information.

This command reports the leakage power in the design. Same as the Report Area command it requires standard libraries.

This command reports the leaf cell type and numbers in the design.

This command reports the hierarchical sub-modules in the design.

This command reports the statistic of the current design. It pops up an option window for interactivity from users.

The command lists the libraries and leaf cells in each library.

This command pops up an entry window for users to input leaf cell name string, wild card can be accepted. All leaf cells matching the string is listed. If there is only one cell matched, the detail property is listed.