This use case demonstrates how to perform a metal-only ECO automatically.

The setup is identical to that of the Automatic Functional ECO case, with the added step of mapping any new gates exclusively to spare gates.

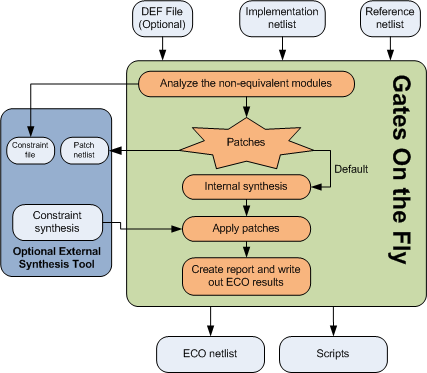

To perform functional ECO, users provide the Implementation netlist that requires modification, as well as a Reference netlist that has been re-synthesized following RTL modification. Additionally, a DEF file may be used to provide physical information.

Utilizing a top-down and global approach, the Internal Logic Equivalent Check engine analyzes the design to identify non-equivalent modules and determine the minimum logic patches required to modify the Implementation netlist during functional ECO. Upon completion of the ECO, the spare gates list is extracted from the Implementation netlist, and the logic patches are mapped exclusively to spare-type gates.

# GofCall ECO script, run_metal_only_example.pl # Any new gates added will be mapped to spare gates use strict; undo_eco; # Discard previous ECO operations # Setup ECO name, had better be unique to avoid naming confliction setup_eco("eco_example"); read_library("art.90nm.lib"); # Read in standard library read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv"); # Read in the Reference Netlist read_design("-imp", "implementation.gv"); # Read in the implementation Netlist Which is under ECO set_top("topmod"); # Set the top module that ECO has been done in the module and its sub-modules read_def("topmod.def"); # Read Design Exchange Format file, optional. # Fix the module 'topmod' and its sub-modules fix_design; # Now we need to map all new added ECO gates to spare type instances # Specify spare cell pattern, when 'map_spare_cells' is done, # a new updated spare list file will be written out. # The updated spare list file has default name 'spare_cells_script_name.list'. # Click 'get_spare_cell' below for more usage detail get_spare_cells("*/*_SPARE*"); # Comment the above line and use the following line to use spare list file # if the spare list file has been generated already and gone through other ECOs # get_spare_cells("-file", "spare_list_file.txt"); map_spare_cells(); # To use external Synthesis Tool # Use RTL Compiler by the following option # map_spare_cells("-syn", "rc"); # Use Design Compiler by the following option # map_spare_cells("-syn", "dc_shell"); report_eco(); # ECO report write_verilog("eco_verilog.v"); # Write out ECO result in Verilog write_soce("eco_soce.tcl"); # Write out TCL script for SOC Encounter exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The above script can be run by '-run' option in GOF command line: