This use case demonstrates how to use GOF to analyze clock trees.

Load in library, LEF, DEF and netlist by the following command

gof -lib tsmc_std.lib -lef tsmc_std.lef -def top.def top.v

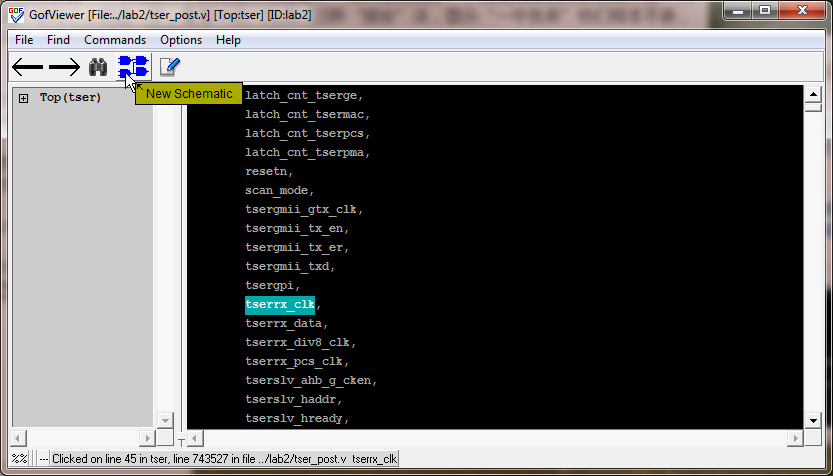

In GofViewer window, search for the clock and click 'New Schematic' button.

Figure 1 Find clock signal and launch New Schematic

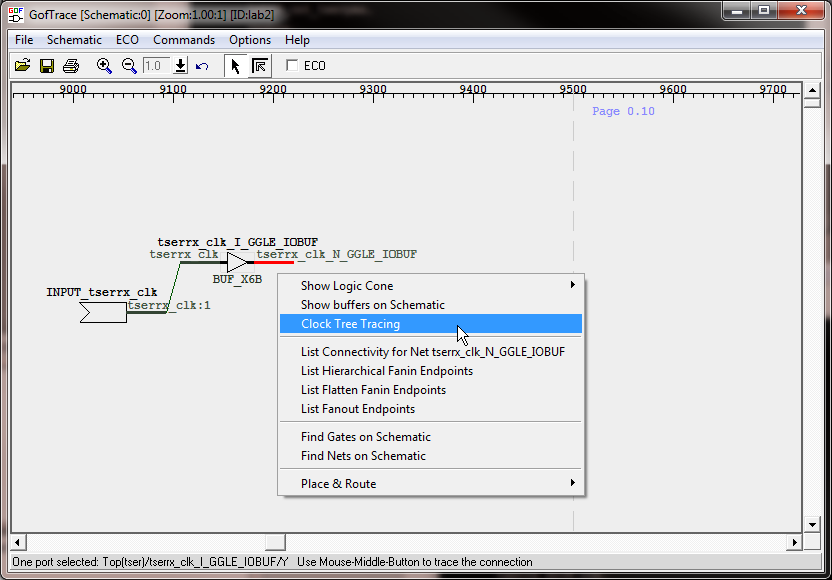

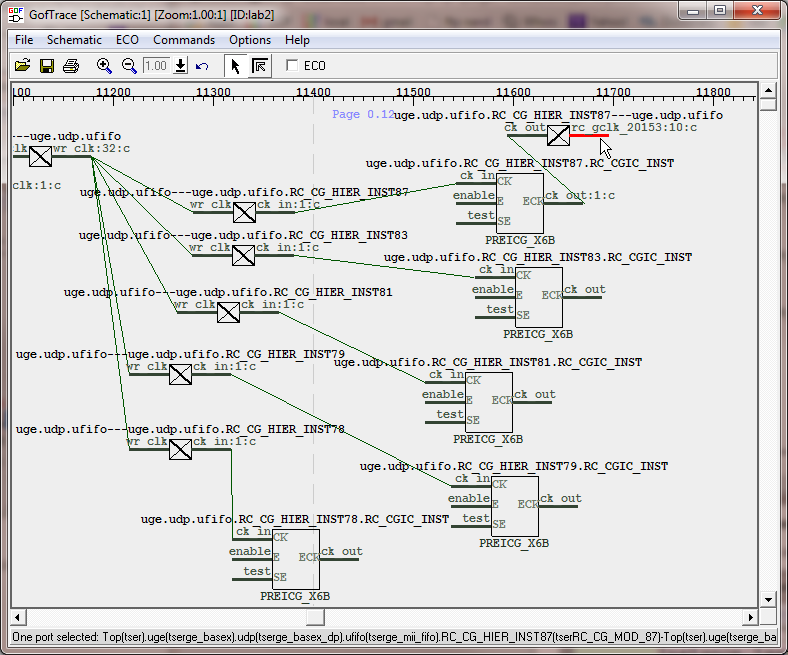

On GofTrace schematic window, click mouse-left-button on any clock cell's output pin to select the pin, click mouse-right-button to popup menu and select 'Clock Tree Tracing' option. Then mouse-middle-button tracing on output pin will bypass flip-flops.

Figure 2 Enable 'Clock Tree Tracing' on schematic

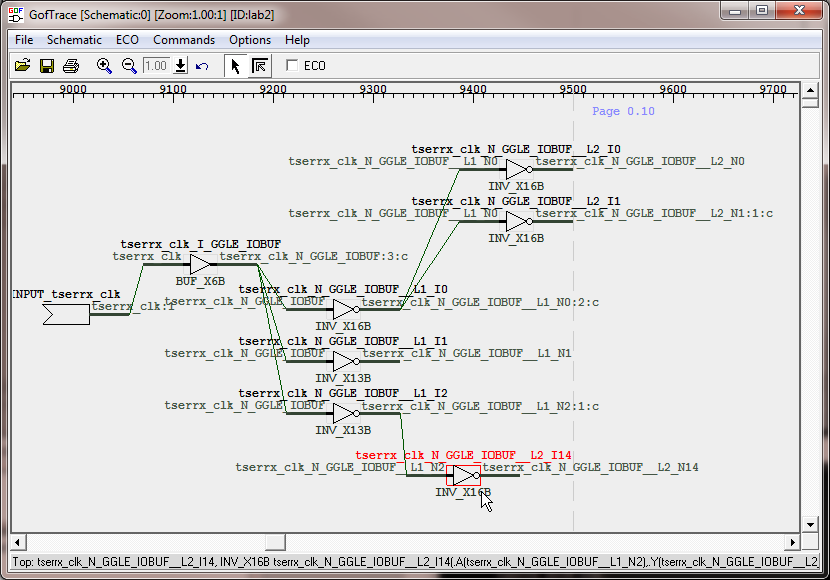

Press mouse-middle-button on cells' output pin to expand the clock tree. The tool puts fanout number and 'c' separated by ':' as suffix on nets driven by clock cells. And flip-flops will be bypassed, since 'Clock Tree Tracing' is enabled in the previous operation.

Figure 3 Tracing Clock Tree

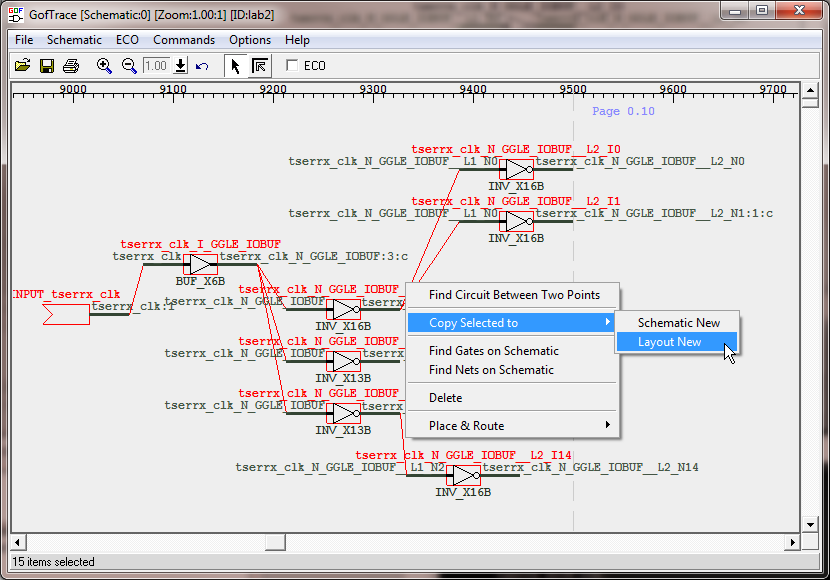

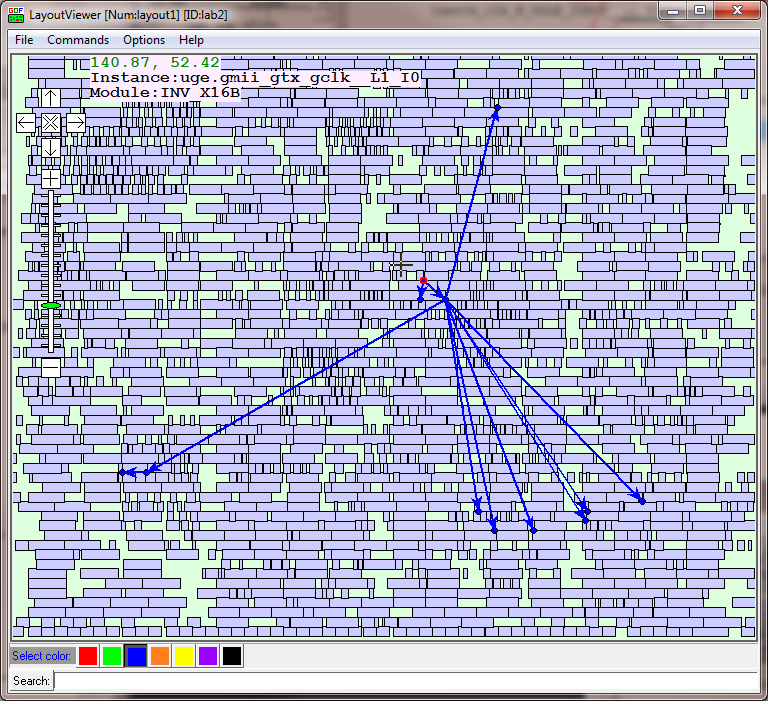

Press ctrl-a, or use mouse to select multiple of objects on the schematic. Click mouse-right-button to popup menu and select 'Copy Selected to'->'Layout New'. The selected circuits' placement will be shown on LayoutViewer window.

Figure 4 Select and send to LayoutViewer

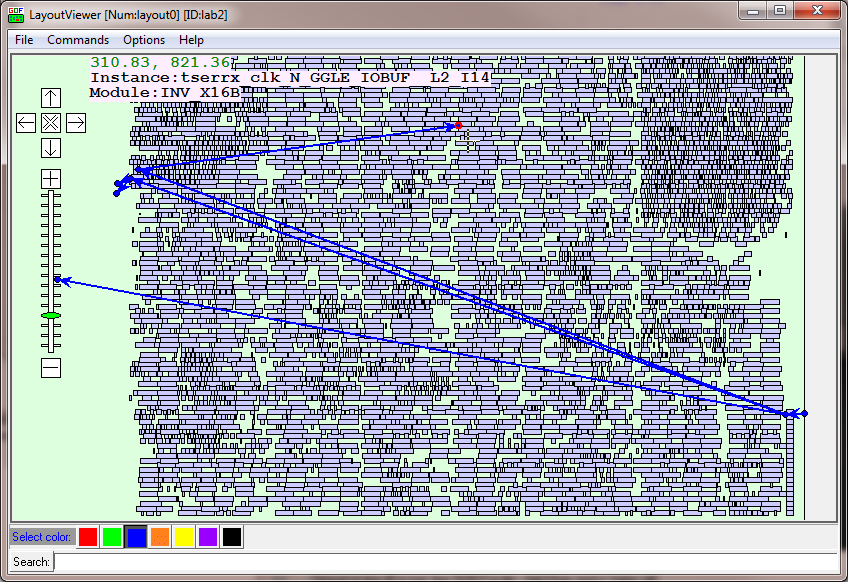

The placement of the clock tree cells and connections are displayed on LayoutViewer window.

Figure 5 Placements and connections are shown on LayoutViewer

Clock tree tracing is wholly under user's control. User decides to expand which branch and the whole clock tree or portion of clock tree can be selected to sent to LayoutViewer for placement and connection analysis.

Figure 6 Clock tree displayed as-needed

Portion of clock tree placements and connections are displayed on LayoutViewer.

Figure 7 Whole or portion displayed on LayoutViewer